# Fortschritt-Berichte VDI

VDI

## Reihe 9

Elektronik/Mikro

und Nanotechnik

Nr. 395

Dipl.-Ing. Matthias Thiele,

Dresden

## Elektromigration und deren Berücksichtigung beim zukünftigen Layoutentwurf digitaler Schaltungen

Technische Universität Dresden

Institut für Feinwerktechnik

und Elektronik-Design

Institutsdirektor Prof. Dr.-Ing. habil. Jens Lienig

ifte

Technische Universität Dresden

# **Elektromigration und deren Berücksichtigung beim zukünftigen Layoutentwurf digitaler Schaltungen**

**Matthias Thiele**

von der Fakultät Elektrotechnik und Informationstechnik der

Technischen Universität Dresden

zur Erlangung des akademischen Grades eines

**Doktoringenieurs**

**(Dr.-Ing.)**

genehmigte Dissertation

Vorsitzender: Prof. Dr.-Ing. habil. Fischer

Gutachter: Prof. Dr.-Ing. habil. Lienig Tag der Einreichung: 15.11.2016

Prof. Dr. rer. nat. Brück Tag der Verteidigung: 09.02.2017

# Fortschritt-Berichte VDI

Reihe 9

Elektronik/Mikro-

und Nanotechnik

Dipl.-Ing. Matthias Thiele,

Dresden

Nr. 395

Elektromigration und

deren Berücksichtigung

beim zukünftigen

Layoutentwurf

digitaler Schaltungen

Technische Universität Dresden

Institut für Feinwerktechnik

und Elektronik-Design

Institutsdirektor Prof. Dr.-Ing. habil. Jens Lienig

**ifTe**

Thiele, Matthias

## **Elektromigration und deren Berücksichtigung beim zukünftigen Layoutentwurf digitaler Schaltungen**

Fortschr.-Ber. VDI Reihe 9 Nr. 395. Düsseldorf: VDI Verlag 2017.

158 Seiten, 58 Bilder, 9 Tabellen.

ISBN 978-3-18-339509-5, ISSN 0178-9422,

€ 57,00/VDI-Mitgliederpreis € 51,30.

**Für die Dokumentation:** Elektromigration – Entwurfsautomatisierung – Finite-Elemente-Methode – Entwurfsregeln – Verdrahtung – Stromdichte – Blech-Länge – CNT – Semiconductor Roadmap

Elektromigration ist momentan einer der begrenzenden Effekte für die Verkleinerung von Strukturgrößen in der Mikroelektronik. Dies begründet sich durch steigende Stromdichten bei sinkenden Leiterquerschnitten. Dadurch sinkt die Zuverlässigkeit der Leitbahnen. Diese Arbeit untersucht Methoden zur Verhinderung von Elektromigrationsschäden im Verdrahtungsentwurf digitaler Schaltkreise mit Strukturgrößen von weniger als 20 nm. Ziel ist es, neue Entwurfsregeln und Strategien für robuste Schaltkreise zu entwickeln. Erstmals steht der Entwurf digitaler Schaltkreise unter Berücksichtigung von Nanotechniken im Mittelpunkt. Es wird gezeigt, dass auch bei weiterer Verkleinerung der Verdrahtungsstrukturen elektromigrationsrobuste Schaltungen möglich sind. Die vorliegende Arbeit wendet sich vorrangig an Ingenieure und Wissenschaftler auf dem Gebiet der Entwurfsautomatisierung.

### **Bibliographische Information der Deutschen Bibliothek**

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliographie; detaillierte bibliographische Daten sind im Internet unter <http://dnb.ddb.de> abrufbar.

### **Bibliographic information published by the Deutsche Bibliothek**

(German National Library)

The Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliographie

(German National Bibliography); detailed bibliographic data is available via Internet at

<http://dnb.ddb.de>.

© VDI Verlag GmbH · Düsseldorf 2017

Alle Rechte, auch das des auszugsweisen Nachdruckes, der auszugsweisen oder vollständigen Wiedergabe (Fotokopie, Mikrokopie), der Speicherung in Datenverarbeitungsanlagen, im Internet und das der Übersetzung, vorbehalten.

Als Manuskript gedruckt. Printed in Germany.

ISSN 0178-9422

ISBN 978-3-18-339509-5

---

# Vorwort

Diese Arbeit entstand im Rahmen meiner Tätigkeit am Institut für Feinwerktechnik und Elektronik-Design (IFTE) zunächst im Graduiertenkolleg „Nano- und Biotechniken für das Packaging elektronischer Systeme“. In meiner anschließenden Zeit als wissenschaftlicher Mitarbeiter am IFTE konnte ich die vorliegende Arbeit fertigstellen. Ich danke meinem Doktorvater Herrn Professor Jens Lienig für die fachkundige Hilfe und Unterstützung sowie für die Geduld in dieser Zeit.

An dieser Stelle möchte ich der Deutschen Forschungsgemeinschaft für die finanzielle Unterstützung sowie Prof. Dr.-Ing. habil. Gerald Gerlach und Frau Dr.-Ing. Bärbel Knöfel für die lehrreiche und schöne Zeit im Graduiertenkolleg danken. Darüber hinaus danke ich den Kollegiaten des Graduiertenkollegs und zahlreichen Mitarbeitern des Instituts für Aufbau- und Verbindungstechnik der Elektronik und des Instituts für Halbleiter- und Mikrosystemtechnik sowie Dr. rer. nat. Paulius Sakalas für die Unterstützung bei der Vorbereitung und Durchführung von Messungen. Für die organisatorische Unterstützung und die fachlichen Diskussionen danke ich insbesondere Prof. Dr.-Ing. Thomas Zerna und Prof. Dr.-Ing. habil. Klaus-Jürgen Wolter. Göran Jerke und Shanthi Siemes danke ich für die Daten aus der Industrie.

Für die vielen hilfreichen Korrekturhinweise während der Erstellung des Manuskripts danke ich besonders Prof. Dr.-Ing. habil. Dr. h. c. Werner Krause, Prof. Dr.-Ing. habil. Jens Lienig, Elisabeth Thiele, Josephine Stapel, Katja Rohatsch, Andreas Krinke und Steve Bigalke.

Prof. Dr.-Ing. habil. Jens Lienig und Prof. Dr. rer. nat. Rainer Brück danke ich für die Begutachtung meiner Dissertation, Prof. Dr.-Ing. habil. Wolf-Joachim Fischer und Prof. Dr.-Ing. Dr. h. c. Karl-Heinz Bock für den Vorsitz bzw. die erfolgreiche Durchführung des Promotionsverfahrens. Ein besonderer Dank gilt meinen Kollegen Dr.-Ing. Frank Reifegerste, Dr.-Ing. Thomas Bödrich und

---

Andreas Krinke, die mit mir das Büro und einige Sorgen teilten und mir oft genug die nötige Motivation gaben, für viele konstruktive Gespräche. Nicht zuletzt danke ich meiner Familie und besonders meiner Frau Elisabeth für den nötigen Rückhalt und die Unterstützung auch in schwierigen Phasen.

---

# Inhaltsverzeichnis

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>1 Einleitung</b>                                                | <b>1</b>  |

| 1.1 Entwicklung der Halbleitertechnologie . . . . .                | 1         |

| 1.2 Entwicklung bei Leitbahnen . . . . .                           | 2         |

| 1.3 Motivation . . . . .                                           | 4         |

| <b>2 Grundlagen</b>                                                | <b>7</b>  |

| 2.1 Elektromigration . . . . .                                     | 7         |

| 2.1.1 Allgemeines zur Elektromigration . . . . .                   | 7         |

| 2.1.2 Möglichkeiten der Quantifizierung . . . . .                  | 8         |

| 2.1.3 Einflussgrößen . . . . .                                     | 11        |

| 2.2 Mechanismen bei der Elektromigration . . . . .                 | 14        |

| 2.2.1 Kristallstruktur und Diffusionsmechanismen . . . . .         | 14        |

| 2.2.2 Barrieren bei Kupfermetallisierungen . . . . .               | 18        |

| 2.2.3 Einfluss durch mechanische Spannungen . . . . .              | 21        |

| 2.2.4 Zusammenspiel der Migrationsarten . . . . .                  | 23        |

| 2.2.5 Frequenzabhängigkeit der EM . . . . .                        | 25        |

| 2.3 Berücksichtigung von EM im Layoutentwurf . . . . .             | 29        |

| 2.3.1 Einordnung in den Layoutentwurf . . . . .                    | 29        |

| 2.3.2 Besonderheiten des digitalen Layoutentwurfs . . . . .        | 31        |

| 2.3.3 Berücksichtigung von EM im digitalen Layoutentwurf . . . . . | 33        |

| <b>3 Zielstellung der Arbeit</b>                                   | <b>36</b> |

| 3.1 Hintergrund und Fragestellungen . . . . .                      | 36        |

| 3.2 Einordnung der Arbeit in den Gesamtkontext . . . . .           | 39        |

| <b>4 Entwicklungstrends bei digitalen Schaltungen</b>              | <b>40</b> |

| 4.1 Mooresches Gesetz und Roadmap ITRS . . . . .                   | 40        |

| 4.2 Verhinderung von EM-Schäden . . . . .                          | 45        |

|                                                                |           |

|----------------------------------------------------------------|-----------|

| <b>5 Methoden für EM-robuste digitale Schaltungen</b>          | <b>47</b> |

| 5.1 Übersicht über die Methoden . . . . .                      | 47        |

| 5.2 Bambus-Effekt . . . . .                                    | 50        |

| 5.2.1 Physikalischer Hintergrund . . . . .                     | 50        |

| 5.2.2 Anwendung . . . . .                                      | 52        |

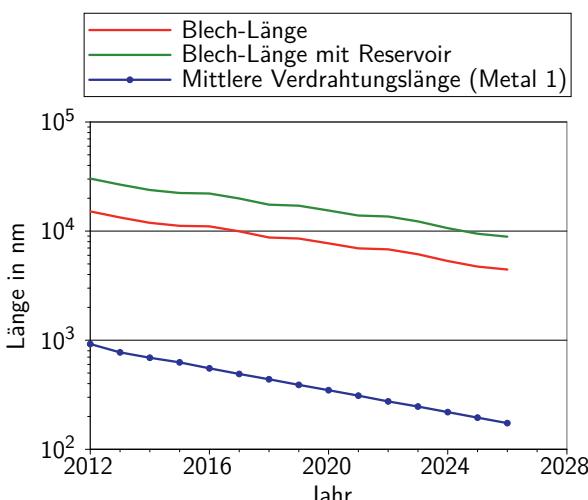

| 5.3 Längeneffekte . . . . .                                    | 55        |

| 5.3.1 Physikalischer Hintergrund . . . . .                     | 55        |

| 5.3.2 Bedeutung für Technologie und Entwurf . . . . .          | 62        |

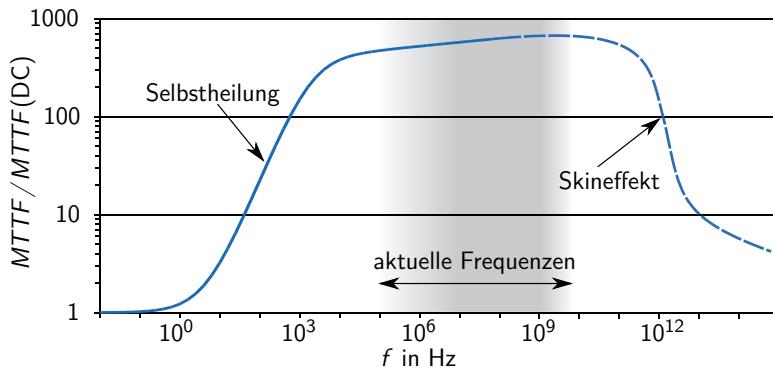

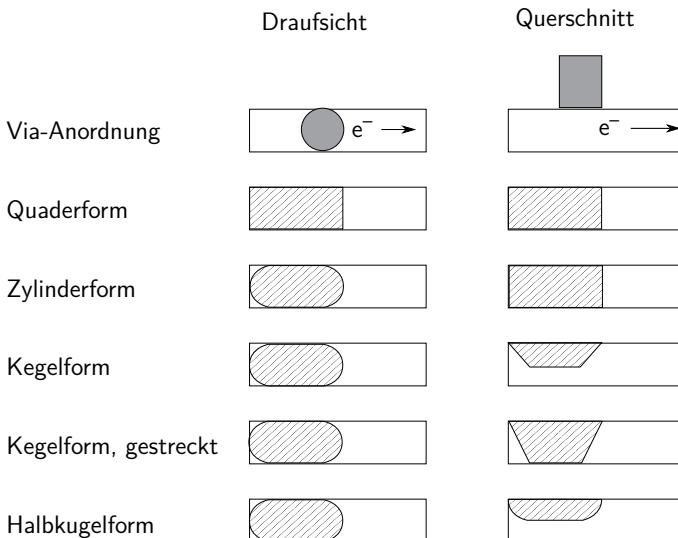

| 5.4 Via-below- und Via-above-Konfigurationen . . . . .         | 67        |

| 5.4.1 Grundlagen . . . . .                                     | 67        |

| 5.4.2 Parameter . . . . .                                      | 68        |

| 5.4.3 Vergleich mit aktuellen Technologien . . . . .           | 69        |

| 5.4.4 Anwendung . . . . .                                      | 69        |

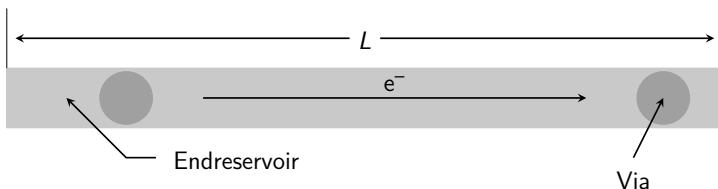

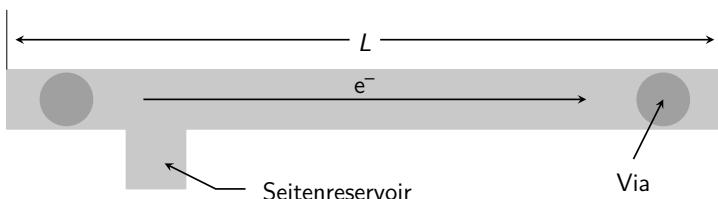

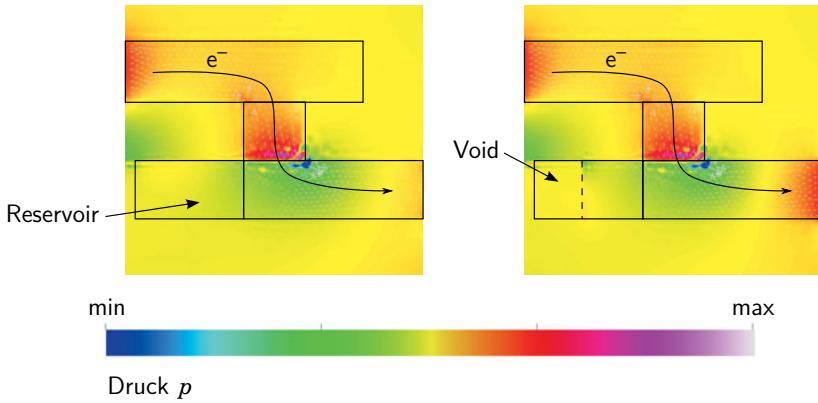

| 5.5 Reservoir . . . . .                                        | 71        |

| 5.5.1 Grundlagen . . . . .                                     | 71        |

| 5.5.2 Quellen und Senken . . . . .                             | 71        |

| 5.5.3 Erscheinungsformen . . . . .                             | 72        |

| 5.5.4 Anwendung . . . . .                                      | 73        |

| 5.6 Mehrfach-Vias . . . . .                                    | 76        |

| 5.6.1 Grundlagen . . . . .                                     | 76        |

| 5.6.2 Stromverteilung . . . . .                                | 77        |

| 5.6.3 Reservoir . . . . .                                      | 78        |

| 5.6.4 Bedeutung der geometrischen Anordnung . . . . .          | 79        |

| 5.6.5 Aktuelle Bedeutung redundanter Vias . . . . .            | 82        |

| 5.6.6 Parameter und Hinweise zur Anwendung bei EM . . . . .    | 82        |

| 5.7 Frequenzabhängige Effekte . . . . .                        | 84        |

| 5.7.1 Selbstheilung und steigende Frequenzen . . . . .         | 84        |

| 5.7.2 Konsequenzen . . . . .                                   | 85        |

| 5.8 Werkstoffe bei klassischer Metallverdrahtung . . . . .     | 87        |

| 5.8.1 Leiterwerkstoff . . . . .                                | 88        |

| 5.8.2 Dielektrikum . . . . .                                   | 89        |

| 5.8.3 Barriere . . . . .                                       | 91        |

| 5.9 Neue Werkstoffe und Technologien . . . . .                 | 95        |

| 5.9.1 Kohlenstoffbasierte Lösungen . . . . .                   | 95        |

| 5.9.2 Eigenschaften der CNT . . . . .                          | 97        |

| 5.9.3 Auswirkungen auf den zukünftigen Layoutentwurf . . . . . | 98        |

|                                                                |            |

|----------------------------------------------------------------|------------|

| 5.10 Zusammenfassung . . . . .                                 | 100        |

| <b>6 Ausgewählte Untersuchungen</b>                            | <b>102</b> |

| 6.1 Simulationsmethoden . . . . .                              | 102        |

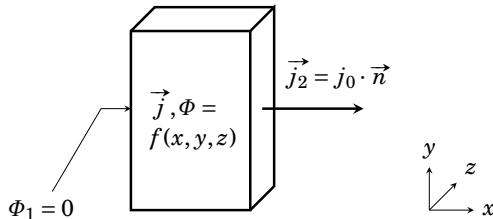

| 6.1.1 Stromdichtesimulation mit Finiten Elementen . . . . .    | 104        |

| 6.1.2 Besonderheiten herkömmlicher Technologien . . . . .      | 106        |

| 6.1.3 Simulation neuer Technologien . . . . .                  | 107        |

| 6.2 Versuchsmethoden der experimentellen Validierung . . . . . | 107        |

| 6.3 Ergebnisse der Untersuchungen . . . . .                    | 111        |

| 6.3.1 Längeneffekte . . . . .                                  | 111        |

| 6.3.2 Reservoirs . . . . .                                     | 117        |

| 6.3.3 Kohlenstoffnanoröhren . . . . .                          | 121        |

| 6.4 Zusammenfassung . . . . .                                  | 124        |

| <b>7 Gesamtzusammenfassung und Ausblick</b>                    | <b>125</b> |

| 7.1 Zusammenfassung der Arbeit . . . . .                       | 125        |

| 7.2 Ausblick: Bibliothek robuster Layoutelemente . . . . .     | 129        |

| 7.3 Ausblick: Nutzung von neuen Technologien . . . . .         | 129        |

| 7.4 Zukünftige Nutzung der Ergebnisse . . . . .                | 130        |

| <b>Glossar</b>                                                 | <b>132</b> |

| <b>Literaturverzeichnis</b>                                    | <b>134</b> |

---

# Abkürzungsverzeichnis

## Bezeichnung   Beschreibung

|      |                                                     |

|------|-----------------------------------------------------|

| ASIC | Application Specific Integrated Circuit             |

| CMP  | Chemical Mechanical Polishing                       |

| CNF  | Kohlenstoffnanofaser                                |

| CNT  | Kohlenstoffnanoröhre                                |

| CVD  | Chemical Vapor Deposition                           |

| EM   | Elektromigration                                    |

| FEM  | Finite-Elemente-Methode                             |

| ILD  | Inter Layer Dielectric                              |

| ITRS | International Technology Roadmap for Semiconductors |

| PC   | Personal Computer                                   |

| REM  | Raster-Elektronen-Mikroskopie                       |

| RFID | Radio-Frequency Identification                      |

| SiP  | System-in-Package                                   |

| SM   | Stressmigration                                     |

| SMU  | Source Measure Unit                                 |

| SoC  | System-on-a-Chip                                    |

| TSV  | Through Silicon Via                                 |

---

# Kurzfassung

Elektromigration ist momentan einer der begrenzenden Effekte für die Verkleinerung von Strukturgrößen in der Mikroelektronik. Ziel der Arbeit ist es, fundierte Vorgaben für den Layoutentwurf digitaler Schaltkreise zu erarbeiten, die es ermöglichen, auch zukünftig elektromigrationsrobuste Schaltungen zu entwerfen. Es werden Möglichkeiten aufgezeigt, wie trotz kleinerer Strukturen eine hohe Elektromigrationsrobustheit erreicht wird. Dazu sind verschiedene Techniken auszunutzen.

Nach dem aktuellen Stand der Technik erreicht die bisherige Technologie in der Mikroelektronik ihre Begrenzung durch Elektromigration. Dies begründet sich durch steigende Stromdichten bei sinkenden Leiterquerschnitten. Dadurch sinkt die Zuverlässigkeit der Leiterbahnen. Mit dieser Arbeit wird gezeigt, dass diese Barriere zu überwinden ist und weitere Verkleinerungen der Strukturen möglich werden. Dabei erfolgt eine Analyse und Zusammenfassung zahlreicher Methoden zur Vermeidung von Elektromigrationsschäden. Die Methoden werden quantitativ analysiert und Vorgaben für den Schaltungs- und Layoutentwurf bei zukünftigen Strukturgrößen erarbeitet. Erstmals wird der Entwurf digitaler Schaltkreise unter Berücksichtigung von Nanotechniken in den Mittelpunkt gesetzt.

Das Thema der Arbeit hat eine herausragende Bedeutung für die zukünftige Entwicklung der Mikroelektronik, da nur durch die Vermeidung der Elektromigration zuverlässige Schaltungen in kleineren Strukturgrößen möglich sind. Es werden Lösungen für aktuelle und zukünftige Probleme im Zusammenhang mit der Elektromigration aufgezeigt. Der direkte Zugriff auf Nanotechniken ermöglicht eine neue Sichtweise auf die Technologien für digitale Schaltungen und erlaubt einen Ausblick in die Zukunft elektromigrationsrobuster Schaltungen.

---

# Abstract

Electromigration is one of the most important constraints for scaling in microelectronics. It is caused by material transport through high current densities in metal interconnects of integrated circuits. While previously only considered in analog circuits and supply nets, it will be an issue also for signal nets of future digital circuits.

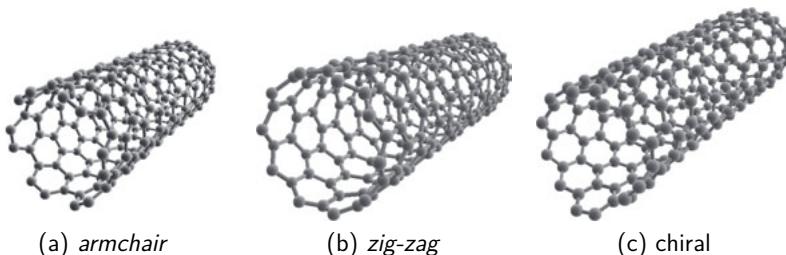

In this thesis, methods preventing electromigration damage in digital integrated circuits are analyzed using finite element analysis and experimental results. The considered methods include the exploitation of bamboo effect, length effect, reservoir effect and material properties. As an outlook, technologies using carbon nanotubes to replace copper interconnects are studied. Finally, specific rules for electromigration robust designs by increasing the current density capability are given.

---

# 1 Einleitung

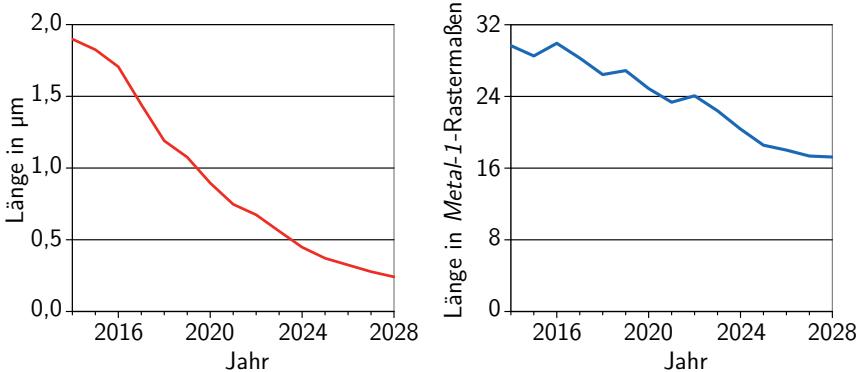

## 1.1 Entwicklung der Halbleitertechnologie

Die Mikroelektronik ist geprägt von der stetigen Reduktion der Strukturgrößen. Aktuell arbeitet man mit Auflösungen von nur einigen zehn Nanometern, und der Trend geht hin zu Strukturen, die sich über immer weniger Atomlagen ausdehnen.

Getrieben wird diese Entwicklung durch zahlreiche Forderungen nach mehr Wirtschaftlichkeit auf verschiedenen Anwendungsgebieten. Kleine Strukturgrößen können zahlreiche Vorteile bieten. Es ist dadurch möglich, bei gleichbleibender Fläche in einem Schaltkreis eine größere Anzahl von Funktionen zu integrieren. Damit übernehmen weniger Schaltkreise mehr Aufgaben. Solche hochintegrierten Schaltkreise bezeichnet man als System-on-a-Chip (SoC), wenn die Schaltung aus lediglich einem Halbleiterchip besteht, oder als System-in-Package (SiP), wenn sie aus mehreren Chips in einem Gehäuse zusammengesetzt ist. Alternativ reduziert sich unter Beibehaltung des Funktionsumfangs die Chipfläche, was durch eine größere Stückzahl pro Wafer zu geringeren Kosten und zu kompakteren Geräten führt.

Ein maßgeblicher Grund für die stetige Verkleinerung ist, dass es auf jedem Wafer eine bestimmte statistische Wahrscheinlichkeit für Defekte gibt. Für einen funktionierenden Schaltkreis muss sich dieser möglichst in einem defektfreien Bereich des Wafers befinden. Kleinere Chips und Transistoren erhöhen die Wahrscheinlichkeit, zwischen den Defekten zu liegen. Dadurch kann die Ausbeute der Schaltkreise gesteigert werden.

Neben diesen offensichtlichen Entwicklungen, die sich allein aus dem Flächenbedarf der einzelnen Transistoren ergeben, entstehen weitere Vorteile. Kleinere Feldeffekttransistoren (FET) besitzen geringere Gate-Kapazitäten, die zum Schalten des Transistors umgeladen werden müssen. Dieses Umladen kann

daher bei gleichbleibendem Strom aufgrund der sinkenden benötigten Ladung mit höherer Frequenz erfolgen.

Einen Überblick über die zukünftigen Halbleitertechnologien gibt die International Technology Roadmap for Semiconductors (ITRS) [ITR14]. Die darin enthaltenen Prognosen ergeben sich aus der Analyse aktuell verfügbarer Techniken und aus der Extrapolation der bisherigen Entwicklung. Sie werden in Kapitel 4 dieser Arbeit ausführlich vorgestellt. Insbesondere können die für die Untersuchung des Elektromigrationsverhaltens wichtigen Parameter, wie die Stromdichte oder Leitbahnbreiten, abgelesen werden.

Laut Prognosen der ITRS [ITR14] steigen die maximal möglichen Taktfrequenzen von Mikroprozessoren von aktuell ungefähr 5,7 GHz auf über 7 GHz im Jahr 2020. Durch diese gesteigerte Taktfrequenz lässt sich die Leistungsfähigkeit eines Schaltkreises zusätzlich zu Funktionserweiterungen erhöhen. Diesem Optimierungsziel entgegengesetzt ist die Verringerung der Verlustleistung, welche sich erreichen lässt, indem man die mögliche Frequenzerhöhung nicht ausreizt, sondern die Ströme verkleinert werden. Zusätzlich kann man kleinere Transistoren mit geringerer Spannung betreiben, was ebenfalls zur Senkung der Verlustleistung beiträgt. Beispielsweise sind die Kernspannungen von Schaltkreisen mit geringer Verlustleistung mittlerweile bei unter 0,7 V angelangt [ITR12].

In der Praxis wählt man je nach Anwendung zwischen den verschiedenen Optimierungszielen ab. Beispielsweise geht es bei mobilen Geräten in erster Linie darum, bei kleiner Chipfläche (hohe Stückzahl) möglichst wenig elektrische Leistung umzusetzen (lange Akkulaufzeit), auch wenn die gegenwärtigen Trends bei Smartphones genau die entgegengesetzten Ziele vermuten lassen. In der überwiegenden Anzahl der Fälle führt die Verkleinerung der Strukturgrößen zu einer positiven Veränderung bei den zu optimierenden Kriterien, was das weitere Voranschreiten in dieser Richtung erklärt.

## 1.2 Entwicklung bei Leitbahnen

Bedingt durch die stetige Verkleinerung von Strukturen auf dem Halbleiterchip ergeben sich weitere Veränderungen der Technologieparameter. Auch diese fol-

gen überwiegend der bereits im Jahre 1965 von Gordon Moore vorausgesagten exponentiellen Entwicklung, selbst wenn er sich lediglich auf einen Parameter, die Anzahl der Transistoren, bezog [Moo65]. Neben dieser Erhöhung der Komplexität sinken Versorgungsspannungen und Ströme in den einzelnen Leitbahnen kontinuierlich. Gleichzeitig sind immer höhere Taktraten technologisch möglich. Genaue Zahlenwerte aus der ITRS enthält Tabelle 4.1 im Abschnitt 4.1.

Neben den oben erwähnten Änderungen in der Technologie, welche direkt aus der Verringerung der Strukturgröße oder zugehörigen technologischen Anpassungen resultieren, beeinflussen Wechsel der Werkstoffe die Eigenschaften von Schaltkreisen sehr stark.

Der Übergang von Aluminium zu Kupfer als Werkstoff für die Leitbahn führte bereits dazu, dass sich deren Ausfallverhalten stark änderte. Einerseits ist Kupfer wesentlich beständiger gegen Migrationsprozesse, andererseits sind nun andere Diffusionspfade von größerer Bedeutung. Zusätzlich neigt Kupfer stärker zur Diffusion in umgebende Dielektrika. Diesem Verhalten ist mit zusätzlichem technologischen Aufwand und verändertem Werkstoffeinsatz zu begegnen. Es werden aktuell verschiedenartige Barriewerkstoffe zwischen Kupfer und dem Dielektrikum erforscht. Daher ist es möglich, dass sich beim Wechsel in eine neue Technologie Barriereeigenschaften sehr stark ändern. Dies wirkt sich auf Eigenschaften wie Aktivierungsenergie an der Oberfläche, mechanische Stabilität des Werkstoffverbunds oder Prozesstemperaturen und damit auf den mechanischen Spannungszustand in den Metallisierungsebenen aus.

Ebenso hat das die Leitbahn umgebende Dielektrikum direkten Einfluss auf die Eigenschaften der Leitbahn. Insbesondere, wenn man Low- $k$ -Werkstoffe anstelle des herkömmlichen Siliziumoxids einsetzt, sind die darin eingebetteten Leitbahnen wesentlich elektromigrationsanfälliger. Durch den bei diesen Werkstoffen kleineren Elastizitätsmodul wirken geringere mechanische Spannungen einer möglichen Extrusion entgegen, was Schäden wahrscheinlicher werden lässt [Tho08].

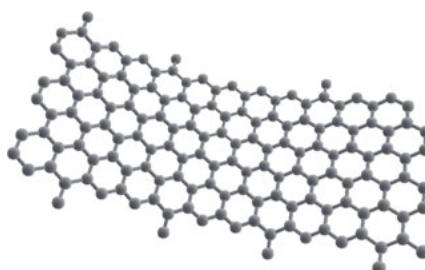

In der ITRS werden auch alternative Werkstoffe betrachtet. Wenn ein genereller Wechsel des Werkstoffes der Leitbahn erfolgt, hat dies weitreichende Konsequenzen für die maßgeblichen Zuverlässigkeitseigenschaften der Verdrahtung. Beispielhaft seien hier die verschiedenen Kohlenstoffkonfigurationen

wie Kohlenstoffnanoröhren (CNT) oder Graphen genannt, die durch ihre hohe Stromtragfähigkeit als Leiterwerkstoffe der Zukunft gelten.

Ebenso beeinflussen Werkstoffe für die vertikalen Verbindungen (Vias) durch ihre Übergänge zu den Leitbahnen den Gesamtaufbau. Auch die Entwicklung hin zu dreidimensionalen Schaltkreisanordnungen verändert durch den Einsatz von *Through Silicon Vias* (TSVs) die Randbedingungen für die Verdrahtungsebenen. Einerseits lassen sich einzelne Bereiche der Chipfläche nicht für die Verdrahtung verwenden, andererseits entstehen in der Nachbarschaft von TSVs Gebiete, in denen mechanische Spannungen auf die Leitbahnen einwirken [PPPL11, PPLP11].

### 1.3 Motivation

Integrierte Schaltkreise zeichnen sich durch ihre im Vergleich zu diskreten Schaltungen höhere Zuverlässigkeit aus. Dieser Vorteil führt zur immer weiteren Verkleinerung von Strukturgrößen und zu den damit verbundenen Investitionen in aufwändige Technologien.

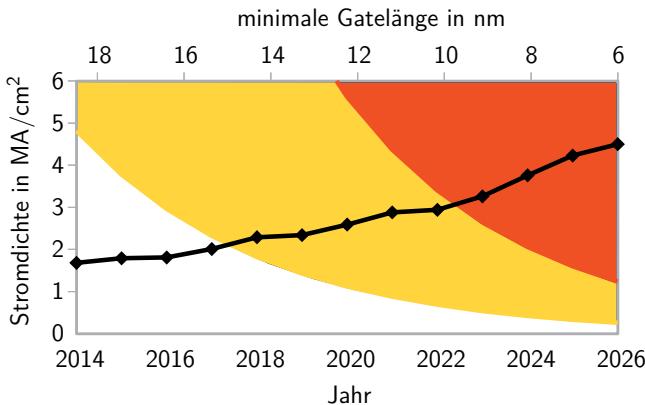

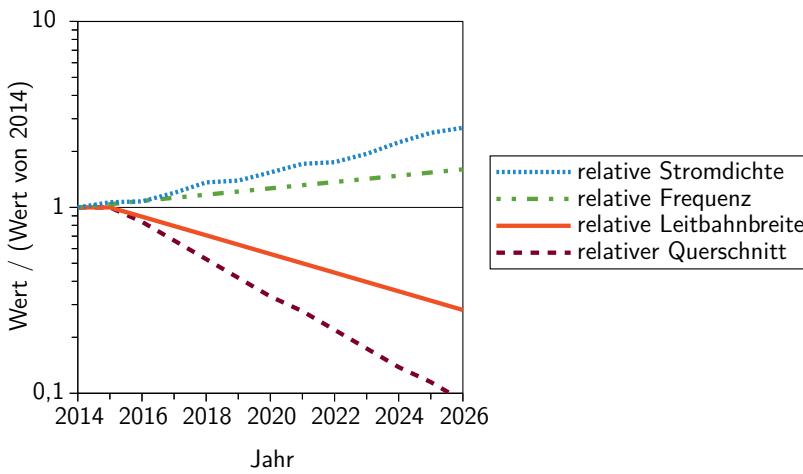

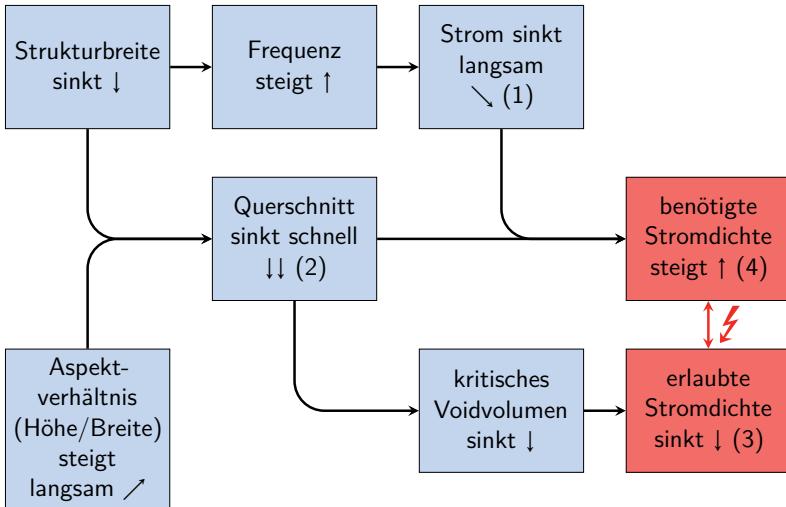

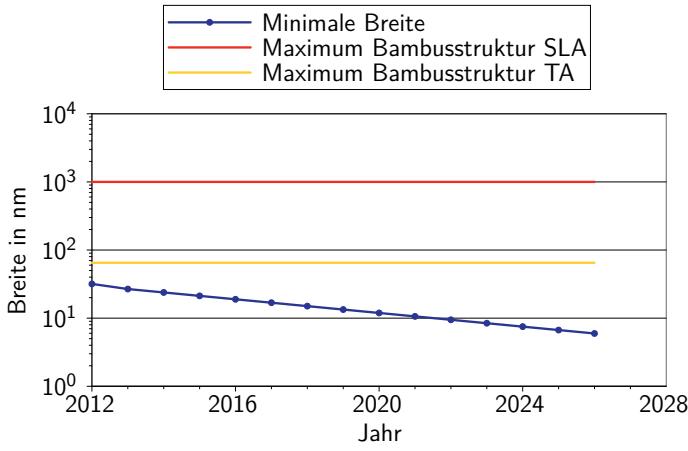

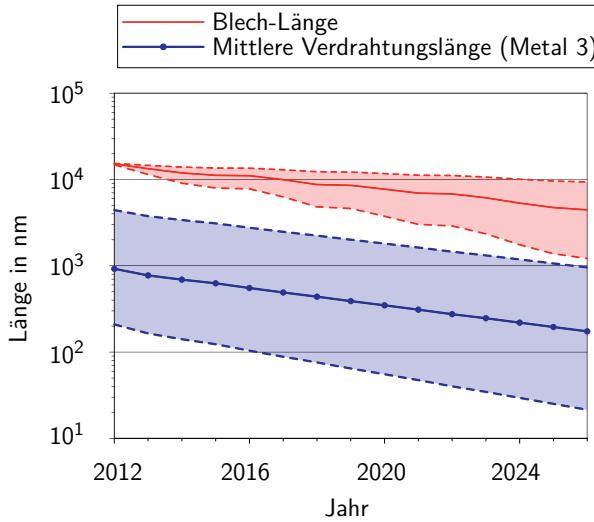

Die verkleinerten Strukturen haben jedoch auch negativen Einfluss auf die Zuverlässigkeit, da sich die Querschnittsflächen der metallischen Leitbahnen in den Schaltkreisen verringern. Gleichzeitig können die benötigten Ströme selbst durch die Verkleinerung der Versorgungsspannungen und Gate-Kapazitäten nicht im gleichen Maß reduziert werden. Dies hat zur Folge, dass die erforderlichen Stromdichten mit jeder Strukturverkleinerung immer weiter steigen (Bild 1.1). Parallel dazu sinken jedoch durch die verringerten Querschnittsflächen der Leitbahnen auch deren erlaubte Stromdichten.

Der hauptsächliche Ausfallgrund für Leitbahnen sind Schäden durch Migrationserscheinungen. Bei hohen Stromdichten tritt insbesondere die Elektromigration (EM) auf, ein Diffusionsprozess in metallischen Leitern, der durch Impulsübertragung der Leitungselektronen ausgelöst wird. Schäden durch EM innerhalb der vorgesehenen Lebensdauer eines Schaltkreises sind zu vermeiden, um die jeweils geforderte Zuverlässigkeit zu erreichen.

Beim Entwurf analoger Schaltkreise sind Maßnahmen gegen Elektromigration, wie stromabhängige Verdrahtung oder die Anpassung der Leitbahnbreite bei

hoch belasteten Leitbahnen, bereits Stand der Technik. Durch weitere Strukturverkleinerungen sind zunehmend auch digitale Schaltkreise von dem Problem steigender Stromdichten und daraus resultierender Elektromigration betroffen. In diesen Schaltungen können die beim Analogentwurf üblichen Methoden, wie das Vergrößern der Leitbahnbreite, nicht angewendet werden. Dies würde der Strukturverkleinerung entgegenwirken und die weitere Skalierung verhindern. Deshalb müssen neue Ansätze entwickelt werden, um EM-Schäden bei digitalen Schaltkreisen trotz weiter sinkender Strukturgrößen zu vermeiden.

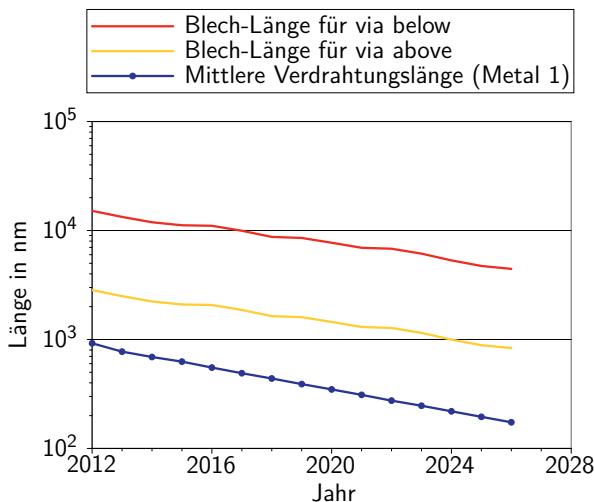

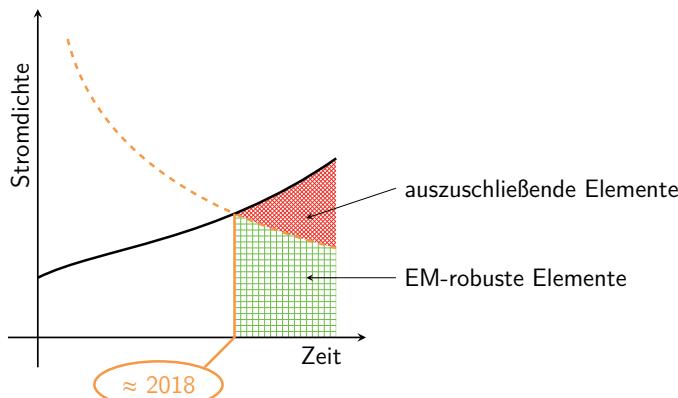

Ziel dieser Arbeit ist es deshalb, Maßnahmen für den Layoutentwurf zu empfehlen, mit denen sich die durch EM verursachten Schäden in digitalen Schaltungen vermeiden lassen. Beispiele hierfür sind die Ausnutzung von Längen- und Reservoireffekten, die elektromigrationsbegrenzend wirken. Für jede Maßnahme sollen Parameter ermittelt werden, anhand derer sich die Anwendbarkeit technologieabhängig feststellen lässt. Zukünftig sind damit die zulässigen Stromdichten an den kritischen Orten durch lokale Layoutveränderungen zu steigern, um dann auch Stromdichten im gelb dargestellten Bereich in Bild 1.1 zu erlauben. Ziel ist es somit, Überschreitungen der zulässigen Stromdichten zu vermeiden, indem diese gezielt vergrößert werden.

**Bild 1.1:** Entwicklung der benötigten Stromdichte zum Treiben von vier Invertern bei fortschreitender Strukturverkleinerung und die dabei abnehmenden Grenzen der zulässigen Stromdichte nach [ITR14]; gelb: Elektromigration muss in allen minimalen Leitbahnen berücksichtigt werden, rot: zur Zeit sind keine EM-robusten technologischen Lösungen bekannt

Folgende neuartige Erkenntnisse werden in dieser Arbeit gezeigt:

- Durch den Einsatz der Finite-Elemente-Methode (FEM) lassen sich zahlreiche Effekte, die die EM beeinflussen, analysieren. Diese sind insbesondere der Längeneffekt und der Reservoir-Effekt.

- Erstmals werden die Maßnahmen zur EM-Vermeidung in herkömmlichen Metallverdrahtungen mit neuen Technologien unter Verwendung von CNT verglichen.

- Der Einfluss verschiedener Maßnahmen auf die zulässige Stromdichte lässt sich durch Simulationen quantisierbar angeben.

- Durch die Anwendung der in dieser Arbeit vorgestellten Maßnahmen lassen sich zukünftig EM-robuste digitale Schaltkreisen entwerfen.

Die untersuchten Maßnahmen müssen bereits bei der Verdrahtung während der Layoutsynthese anwendbar sein, da sich durch geeignete Verdrahtung die bestmögliche Ausnutzung der Effekte zur Steigerung der Zuverlässigkeit erreichen lässt. Methoden, die erst später eingreifen und das Layout nachträglich verändern, sind wesentlich ineffektiver, weil dabei weniger Spielraum für entsprechende Veränderungen besteht.

Zur theoretischen Ermittlung der Stromdichte wird hauptsächlich auf die FEM zurückgegriffen, durch die sich eine große Anzahl von physikalischen Einflüssen an Modellen beliebiger Geometrie erfassen lässt.

Im nachfolgenden zweiten Kapitel wird zunächst ein Überblick über das Problem der Elektromigration und dessen Berücksichtigung im Schaltkreisentwurf gegeben, bevor das dritte Kapitel auf das Ziel der gesamten Arbeit näher eingeht. Das vierte Kapitel leitet aus der Analyse der Technologieentwicklung verschiedene Methoden für elektromigrationsrobuste Leitbahnen ab, die anschließend im fünften Kapitel detailliert beschrieben werden. Weiterhin sind darin zukünftige Trends für die einzelnen Methoden erarbeitet.

Kapitel 6 stellt die Untersuchungsergebnisse aus Simulationen und Experimenten zu den vorgestellten Methoden für robustere Leitbahnen dar. Es zeigt auf, welche Maßnahmen in zukünftigen Schaltkreisen eingesetzt werden können. Darüber hinaus beschreibt das Kapitel die Theorie zu neuartigen Analysemethoden für Elektromigrationserscheinungen. Das letzte Kapitel fasst die Arbeit zusammen und gibt einen Ausblick auf zukünftige Arbeiten sowie mögliche Entwicklungen der Verdrahtungen in der Mikro- und Nanoelektronik.

## 2 Grundlagen

### 2.1 Elektromigration

#### 2.1.1 Allgemeines zur Elektromigration

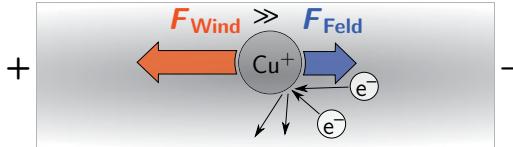

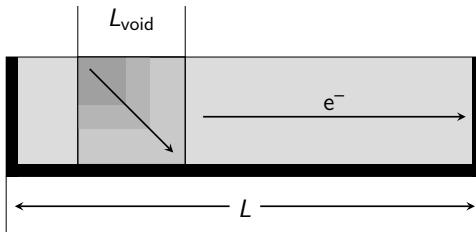

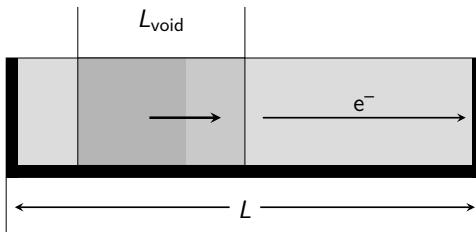

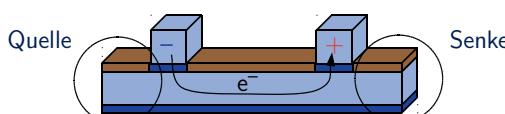

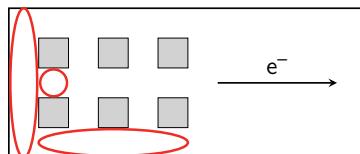

Elektromigration (EM) ist ein Prozess in den metallischen Leitbahnen integrierter Schaltkreise, der negative Auswirkungen auf die Zuverlässigkeit hat und durch hohe Stromdichten verursacht wird. Die geläufige Erklärung für EM ist der Impulsaustausch zwischen Leitungselektronen und den Metallionen (Bild 2.1). Dieser erzeugt eine Kraft  $F_{\text{Wind}}$ , den Elektronenwind, die der elektrostatischen Kraft  $F_{\text{Feld}}$  aus dem Feld im Leiter entgegengesetzt ist.

**Bild 2.1:** Metallionen, die die Gitterstruktur einer Leitbahn bilden, sind beim Stromfluss zwei Kräften ausgesetzt. EM resultiert aus der dominanten Kraft  $F_{\text{Wind}}$ , die durch die Impulsübertragung von bewegten Leitungselektronen auf die Metallionen hervorgerufen wird.

Die Kraft des elektrostatischen Feldes auf die Metallionen wird durch die umgebenden Elektronen größtenteils kompensiert, sodass die resultierende Kraft in Richtung des Elektronenwindes wirkt. Überschreitet die Kraft und damit auch die auf die Ionen übertragene Energie eine bestimmte Schwelle, die Aktivierungsenergie  $E_a$ , beginnt ein gerichteter Diffusionsprozess. Der Stofftransport findet in Richtung der Elektronenbewegung, also von der Kathode (-) zur Anode (+) statt. Die genauen Diffusionspfade sind werkstoffabhängig und werden vorrangig durch die Größe ihrer jeweiligen Aktivierungsenergien bestimmt. Jeder Werkstoff besitzt unterschiedliche Aktivierungsenergien für die Diffusion im

Kristall, entlang von Korngrenzen und an Oberflächen (siehe Abschnitt 2.1.3). Die Relationen zwischen den einzelnen Beträgen bestimmt, welcher Diffusionsmechanismus dominiert und wie sich der gesamte Diffusionsfluss zusammensetzt.

Wenn man den Stofftransport an jedem Ort der Verdrahtung als homogen annehmen könnte, käme es effektiv zu keiner Veränderung der Leitbahn. Es würde stets soviel Werkstoff nachgeliefert wie abtransportiert wird. Da aber die Verdrahtung eines funktionierenden Schaltkreises eine Vielzahl an Inhomogenitäten enthält, entsteht auch eine inhomogene Diffusion. Die genannten Inhomogenitäten bestehen aus

- Enden von Leitbahnen,

- Richtungsänderungen von Leitbahnen,

- Ebenenwechseln,

- inhomogenen Stromdichten aufgrund von Änderungen des Leitbahnquerschnitts,

- Änderungen des Gefüges oder des Werkstoffs,

- Vorschäden oder Fertigungstoleranzen,

- inhomogenen Temperaturverteilungen oder

- mechanischen Spannungsgradienten.

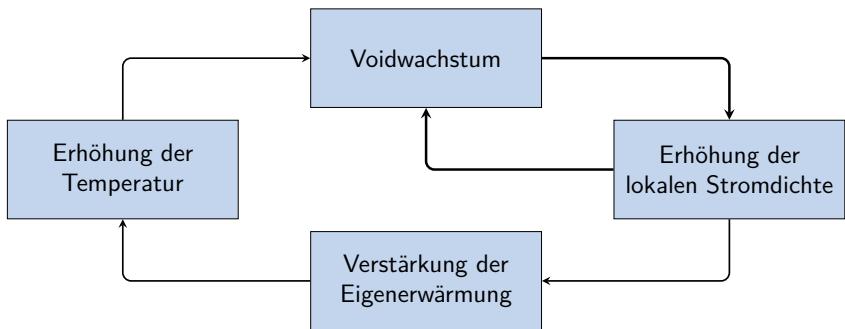

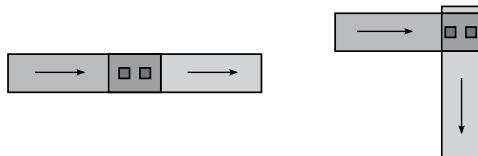

Daraus resultieren Divergenzen im Diffusionsfluss, die zur Verarmung oder Anreicherung von Metall führen. Dabei entstehen Schäden durch Hohlräume (*Voids*) und Unterbrechungen der Leitbahn oder durch Ansammlungen (*Hillocks*, Hügeln), die Kurzschlüsse hervorrufen können. Problematisch an diesem Schädigungsprozess ist insbesondere, dass er positive Rückkopplungen besitzt und sich deshalb selbst beschleunigt (Bild 2.2). So verstärkt die Stromdichte das Voidwachstum und die entstehende Querschnittsschwächung steigert die lokale Stromdichte. Gleichzeitig sorgt die Stromdichte über die Eigenerwärmung für eine Temperaturerhöhung, die die Diffusion und somit das Voidwachstum ebenfalls beschleunigt.

### 2.1.2 Möglichkeiten der Quantifizierung

Zur quantitativen Analyse von EM-Prozessen kann zunächst die Diffusionsgleichung (siehe Abschnitt 2.2.1) verwendet werden, um die Divergenz des Stoffflus-

ses zu bestimmen. Daraus ergeben sich die Orte mit Materialanreicherung und -verarmung, bei denen voraussichtlich zuerst Schäden entstehen. Darüber hinaus lässt sich eine mittlere Lebensdauer der Leitbahn bestimmen. Berechnungen dieser Art sind jedoch nur für sehr einfache Fälle mit vertretbarem Aufwand durchzuführen. Bereits zur Bestimmung der Lebensdauer sind mehrere Iterationen und numerische Verfahren nötig. Ähnlich verhält es sich bei komplexeren Geometrien. Schon bei einer einzelnen Richtungs- oder Querschnittsänderung kann sich eine numerische Simulation als notwendig erweisen.

Für einfache lineare Leitbahnen existiert ein empirisches Modell zur Bestimmung der mittleren Lebensdauer *MTTF* (*Mean Time to Failure*). Das ist die Zeit, nach der statistisch  $1 - e^{-1} \approx 63\%$  der Leitbahnen ausgefallen sind. Dieses wird durch die Black'sche Gleichung beschrieben, die J. R. Black in den 1960er Jahren aufstellte [Bla69]. Die Gleichung

$$MTTF = \frac{A}{j^2} \cdot \exp\left(\frac{E_a}{k \cdot T}\right) \quad (2.1)$$

zeigt die ursprüngliche Form.

Dabei ist  $A$  ein Parameter, der von der Leitbahngeometrie abhängt und in den die Querschnittsfläche der Leitbahn eingeht,  $j$  die Stromdichte,  $E_a$  die Aktivierungsenergie,  $k$  die Boltzmann-Konstante und  $T$  die Temperatur. In späteren Varianten wurde der konstante Exponent (2) der Stromdichte durch die Variable  $n$  ersetzt, wodurch eine Anpassung des Modells auf unterschiedlich

**Bild 2.2:** Beschleunigung des Wachstums von Hohlräumen (Voids) durch positive Rückkopplung bei der EM

dominierte Ausfallmechanismen möglich ist. Konkret bedingt dies jeweils andere Exponenten für verschiedene Leiterwerkstoffe wie Aluminium oder Kupfer.

Für Aluminium und die dabei dominierende Korngrenzendiffusion beträgt die Aktivierungsenergie ungefähr 0,7 eV bei einem Stromdichteeexponenten von  $n = 2$ . Kupfer hingegen besitzt die geringste Aktivierungsenergie mit 0,9 eV bei der dominierenden Oberflächendiffusion mit einem Stromdichteeexponenten zwischen 1,1 und 1,3, je nach vorherrschendem Mechanismus der Voidentstehung [FWB<sup>+</sup>09].

Die Black'sche Gleichung bietet eine relativ einfache Möglichkeit, die Abhängigkeit der Lebensdauer von Strom und Temperatur abzuschätzen. Speziell lassen sich mit Hilfe der Gleichung Aussagen für beschleunigte Tests ableiten. Einschränkend muss jedoch erwähnt werden, dass eine starke Erhöhung des Stroms, und somit der Stromdichte, eine Änderung des Ausfallmechanismus zur Folge hat, die nicht von der Gleichung erfasst wird. Es entstehen dann zusätzlich große Temperaturgradienten durch die Eigenerwärmung der Leitbahn, die eine Thermomigration (siehe Abschnitt 2.2.4) oder gar ein thermisches Versagen zur Folge haben können.

Eingeschränkt lässt sich die Black'sche Gleichung zur Dimensionierung von Leitbahnen für gewünschte Zuverlässigkeit nutzen. Der maßgebliche Nachteil ist, dass die Gleichung für geradlinige Leitbahnen entwickelt wurde und sich die Aussagen nicht direkt auf komplettete Netze mit Richtungsänderungen oder Ebenenwechseln übertragen lassen. Übergänge zwischen verschiedenen Werkstoffen und mechanische Randbedingungen bleiben unberücksichtigt, sodass eine Übertragbarkeit zwischen unterschiedlichen Technologien nicht gegeben ist. Insbesondere die Parameter  $A$  und  $E_a$  sind technologiespezifisch.

Li und Tan entwickelten in [LT11] ein weiteres, komplexeres Modell für die Berechnung der Lebensdauer, das mehr Randbedingungen wie thermischen und mechanischen Stress berücksichtigt. Gleichzeitig beinhaltet dieses Modell, das auf der Eyring-Gleichung basiert, wesentlich mehr Parameter. Deren Bestimmung ist im Vergleich zur Black'schen Gleichung erleichtert, da das Modell stärker physikalisch basiert ist. Die Parameter der Black'schen Gleichung hingegen sind rein empirisch definiert und lassen sich nur durch statistische Untersuchungen bestimmen.

### 2.1.3 Einflussgrößen

Die Einflussgrößen und Randbedingungen der EM kann man in drei Gruppen einteilen. Die Ursprünge der Einflussgrößen sind

- a) die Technologie, speziell die Werkstoffe,

- b) die Umwelt, insbesondere die Temperatur und

- c) der Entwurf, der maßgeblich auf die Stromdichte einwirkt.

Diese Gruppen sollen nachfolgend detailliert betrachtet werden.

#### a) Technologie

Die wichtigste Eigenschaft des Leiterwerkstoffes ist die Aktivierungsenergie  $E_a$ . Sie ist ein Maß für den Widerstand der Metallionen gegen EM bzw. Diffusion im Allgemeinen. Die Aktivierungsenergie wird in erster Linie durch die Bindungsenergie des Metallgitters bestimmt. Deshalb gelten grundsätzlich für verschiedene Leiterwerkstoffe, wie Kupfer und Aluminium, unterschiedliche Werte. Darüber hinaus sind die Metallionen innerhalb eines Werkstoffgefüges unterschiedlich stark gebunden. Die stabilste Bindung mit der höchsten Aktivierungsenergie existiert im Inneren der Kristallite. Dort sind die Ionen nur in der Nähe von Kristallbaufehlern, wie Fehlstellen (Vakanzen) oder Versetzungen, in der Lage, ihre Position zu verlassen. In polykristallinen Leitbahnen sind die Ionen an den Korngrenzen schwächer gebunden und besitzen eine geringere Aktivierungsenergie, weil eine Asymmetrie der Bindungskräfte vorliegt. Ebenso verhält es sich an den äußeren Begrenzungen oder Oberflächen der Leitbahn, wobei hier die Werkstoffe in der Umgebung einen entscheidenden Einfluss auf die Aktivierungsenergie haben. Bei Aluminium ist die Aktivierungsenergie an den Korngrenzen am geringsten, weshalb die Korngrenzendiffusion dominiert. Durch Dotierung, zum Beispiel mit Kupfer, oder durch gezieltes Erzeugen großer Körner lässt sich deshalb eine signifikante Steigerung der EM-Robustheit erreichen. Bei Kupfer dominiert hingegen die Grenz- oder Oberflächendiffusion. Aus diesem Grund wird sehr viel in die Erforschung von Barriereförderwerkstoffen zum Steigern der Aktivierungsenergie investiert.

Die Umgebung der Leitbahnen beeinflusst nicht nur die Aktivierungsenergie der Oberflächendiffusion, sondern auch die mechanischen Randbedingungen. Unter

dem Einfluss mechanischer Spannungen kann EM durch entgegengerichtete Stressmigration gestoppt werden. Dabei spielen weniger die Barrierewerkstoffe als hauptsächlich die Dielektrika eine entscheidende Rolle. Nur bei ausreichend großen mechanischen Spannungsgradienten kann eine nennenswerte Stressmigration einsetzen. Deshalb sind Dielektrika mit hohen Elastizitätsmoduln zu bevorzugen. Das durch die Technologie vorgegebene Dielektrikum beeinflusst hier das EM-Verhalten

Technologische Einschränkungen geben Randbedingungen für den Layoutentwurf vor, die man als Entwurfsregeln (*Design Rules*) bezeichnet. Damit ergeben sich zwangsläufig bestimmte geometrische Konfigurationen mit Bedeutung für das EM-Verhalten. Dabei hat der Entwurf selbst kaum noch Einfluss auf diese Konfigurationen. Die technologischen Vorgaben für den Entwurf sind im Allgemeinen Abstands-, Überlappungs- und Breitenregeln. Daneben bestehen weitere Regeln für die Flächenverhältnisse zwischen Metall und Dielektrikum auf jeder Verdrahtungsebene. Bestimmte Maße, wie die Schichtdicke der einzelnen Ebenen oder die Größe von Vias, sind meist von der Technologie vorgegeben.

### b) Umwelt

Die wichtigste Umwelt-Einflussgröße ist die Temperatur, wie man schon aus Gleichung (2.1) ablesen kann. Dabei spielt das Anwendungsgebiet des Schaltkreises die entscheidende Rolle. So sind es vor allem Schaltkreise der Automobilelektronik, für die die höchsten Temperaturanforderungen gelten. Die Auslegung für Umgebungstemperaturen bis zu 175 °C ist dabei die Regel, wobei solche Werte im Betrieb durchaus erreicht werden können, insbesondere im Motorraum von Verbrennungskraftfahrzeugen.

Hohe Verlustleistungen, die bei digitalen Schaltkreisen, wie Mikroprozessoren oder bei analogen Verstärkern auftreten, können ebenfalls für ähnliche Temperaturbelastungen sorgen. Insbesondere, wenn hohe Verlustleistungen mit hohen Umgebungstemperaturen zusammentreffen, sind starke Alterungerscheinungen der Schaltkreise wahrscheinlich.

Die Temperaturbelastung verstärkt die EM, da ein Teil der Aktivierungsarbeit durch thermische Energie bereitgestellt wird. Zusätzlich wird der Diffusionsprozess durch die erhöhte Beweglichkeit der Atome beschleunigt. Kupfer reagiert

besonders sensibel auf Temperaturänderungen. Eine Erhöhung der Arbeitstemperatur um 10 K sorgt dafür, dass der Strom auf weniger als die Hälfte zu reduzieren ist, um die gleiche Lebensdauer zu erreichen. Dieser Zusammenhang lässt sich aus Gleichung (2.1) ableiten. Ein weiterer Faktor, der thermisch zu beachten ist, ist die Eigenerwärmung der Leitbahn bei hohen Stromdichten (*Joule Heating*). Sie führt zusätzlich zu Temperaturgradienten in der Leitbahn, die eine Thermomigration hervorrufen.

Neben der Temperatur sind es vor allem verschiedene Substanzen, die durch Diffusion in die Metallisierung eindringen können und den Elektromigrationsprozess beeinflussen. Wenn beispielsweise Wasser in die Verdrahtung eindringt, kann eine elektrolytische Migration auftreten. Sauerstoff hingegen beeinflusst die Prozesse durch Oxidation der Metalle. Dies sind maßgebliche Änderungen des gesamten Prozesses, welche normalerweise zu sehr schneller Zerstörung führen. Da sich diese Diffusion von Fremdstoffen durch geeignete Barrieren unterbinden lässt, sollen derartige Umwelteinflüsse nachfolgend nicht näher betrachtet werden.

### c) Entwurf

Der Entwurf selbst beeinflusst die EM überwiegend durch Vorgabe der Stromdichte. Diese, als Quotient aus Strom und Querschnittsfläche, wird durch die Schaltungstechnik und die Verdrahtung bestimmt. Die von der Schaltung geforderten Ströme sind zu übertragen. Dabei ist jede Leitbahn in ihrer Breite an den Strom anzupassen. Daneben entstehen durch Richtungsänderungen und Ebenenwechsel lokal erhöhte Stromdichten, die zu verstärkter EM und der Agglomeration von Schäden führen. Alle durch den Layoutentwurf beeinflussbaren geometrischen Strukturen, die also nicht ausschließlich durch die Technologie vorgegeben sind, können genutzt werden, um die elektromigrationsbegrenzte Lebensdauer der Verdrahtung zu steigern. Neben der Vermeidung hoher lokaler Stromdichten sind weitere Einflüsse auf die EM zu nutzen. Insbesondere die Länge der Leitbahnen kann sinnvoll zur Erhöhung der Lebensdauer beitragen, wenn die Blech-Länge [Ble76] ausgenutzt wird. Dabei wirkt die mechanische Stressmigration bei Leitbahnen unterhalb einer kritischen Länge der EM entgegen und verhindert das Entstehen von Schäden (siehe Abschnitt 2.2.4 und Abschnitt 5.3).

Neben der Stromdichte hat die Frequenz als weitere, durch den Entwurf bestimmte Größe, Einfluss auf die Zuverlässigkeit der Leitbahnen. Durch die Richtungsänderung des Stroms kehrt sich die Diffusionsrichtung ebenfalls um und entstandene kleine Vorschädigungen der Leitbahn werden teilweise behoben. Dieser Vorgang wird als Selbstheilung bezeichnet und ist stark von der Frequenz des Stroms abhängig (siehe Abschnitt 2.2.5 und Abschnitt 5.7).

### Bewertung der drei Teilbereiche

Technologische Aspekte sind bereits vielfach Gegenstand der Forschung. Auch hat der Schaltungsentwickler darauf wenig Einfluss. Ebenso ergeben sich die Temperaturen hauptsächlich aus dem kaum vorhersagbaren Einsatzgebiet des Schaltkreises. Der letzte Abschnitt 2.3 dieses Kapitels beschreibt deshalb aktuelle Methoden zur Berücksichtigung von EM im Entwurf, die im späteren Teil der Arbeit wieder aufgegriffen und erweitert werden.

## 2.2 Mechanismen bei der Elektromigration

### 2.2.1 Kristallstruktur und Diffusionsmechanismen

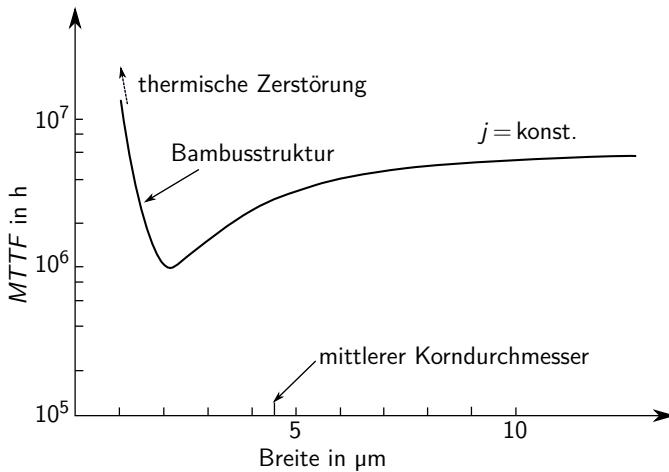

Leitbahnen integrierter Schaltkreise unterscheiden sich in ihrer Gefügestruktur (Bild 2.3). Die häufigste Form des Gefüges metallischer Leitbahnen sind polykristalline, feinkörnige Strukturen. Theoretisch können auch, abhängig vom Verhältnis zwischen der Korngröße und den Abmessungen der Leitbahn, polykristalline Leitbahnen aus wenigen Körnern, Bambusstrukturen, Einkristalle sowie amorphe Strukturen auftreten.

In amorphen Strukturen existieren weder Korngrenzen noch kristalline Bereiche, daher zeigen sich hier sehr spezielle Eigenschaften des Werkstoffs. Da keine *Fernordnung*<sup>1</sup> vorhanden ist, können Diffusionskanäle wie im regulären Kristallgitter nicht entstehen. Der Zusammenhalt und die Atomdichte unterscheiden sich vom kristallinen Zustand. Allerdings lassen sich Metalle nur unter extremen Bedingungen, wie Abkühlgeschwindigkeiten von  $10^5$  K/s bis  $10^6$  K/s,

<sup>1</sup>periodische Anordnung von Atomen über viele Atome hinweg, wie in einem regelmäßigen Gitter

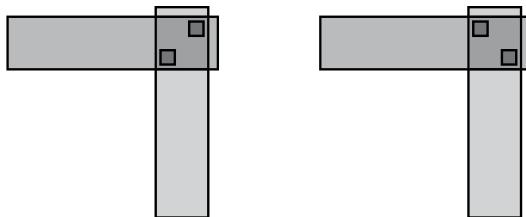

| Gefügeart      | Schematische Darstellung | Besonderheiten                                             |

|----------------|--------------------------|------------------------------------------------------------|

| amorph         |                          | weder Kristallgitter noch Korngrenzen vorhanden            |

| polykristallin |                          | Korngrenzen dominieren                                     |

| bambusähnlich  |                          | Eigenschaften von Kristallgitter und Korngrenzen abhängig  |

| bambusartig    |                          | Kristallgitter dominiert                                   |

| einkristallin  |                          | Kristallgitter und Gitterstörungen bestimmen Eigenschaften |

**Bild 2.3:** Verschiedene Mikrostrukturen bei metallischen Leitbahnen

in den amorphen Zustand überführen [SW96]. Solche Bedingungen sind im Herstellungsprozess integrierter Schaltkreise nicht zu erreichen. Das andere Extrem, der einkristalline Zustand, ist ebenfalls nur mit großem technischen Aufwand erzielbar. Meistens ist es dazu erforderlich, den Kristall aus einem einzelnen Keimling in der Schmelze zu züchten. Dieser Vorgang ist innerhalb einer Leitbahn, die von unterschiedlichen Werkstoffen umgeben ist, nahezu unmöglich. Eine Variante, die unterhalb der Schmelztemperatur funktioniert, wurde in [JT97] verwendet. Dabei konnten Aluminium-Einkristalle auf einer einkristallinen Natriumchloridschicht erzeugt werden. Gleichzeitig ermöglicht dieses Verfahren die gezielte Ausprägung unterschiedlicher Kristallorientierungen. Allerdings eignet sich diese Technologie nur für den Laboreinsatz und nicht für die Schaltkreisherstellung, auch wegen des in den Halbleiterprozessen unerwünschten Natriumchlorids. Problematisch ist bei Einkristallen zudem, dass einzelne Kristallbaufehler die Eigenschaften der Leitbahn stark beeinflussen können. Dies widerspricht der geforderten Prozessstabilität, die für die Zuverlässigkeit wichtig ist.

Deshalb ist der polykristalline Zustand in Leitbahnen die Regel. Hierbei treten sehr unterschiedliche Arten von polykristallinen Strukturen auf, die sich in ihren Eigenschaften in Bezug auf die EM grundlegend unterscheiden können. In

feinkörnigen polykristallinen Gefügen kann sowohl Volumen- bzw. Gitterdiffusion (*Bulk Diffusion*) als auch Korngrenzendiffusion (*Grain Boundary Diffusion*) stattfinden. Zusätzlich besteht unabhängig vom Gefüge die Möglichkeit der Oberflächen- oder Grenzflächendiffusion (*Surface Diffusion*), auf die später eingegangen wird.

Für die EM gelten zunächst, wie für alle anderen Migrationsarten, die Diffusionsgesetze. Aus der eindimensionalen Diffusionsgleichung (Wärmeleitungsgleichung) für homogene Medien

$$\frac{\partial c}{\partial t} = D \cdot \frac{\partial^2 c}{\partial x^2} \quad (2.2)$$

mit der Konzentration  $c$ , der Zeit  $t$ , der Diffusionskonstanten  $D$  und dem Ort  $x$  lässt sich für die EM eine vereinfachte Betrachtung für ein Metallgefüge ableiten. Die Diffusionsgeschwindigkeit  $v$  der Atome, die von der Stromdichte angeregt wird, errechnet sich nach [AN91] durch

$$v = \frac{D}{kT} \cdot ez^* \varrho j \quad (2.3)$$

beschrieben. Dabei ist  $k$  die Boltzmann-Konstante,  $T$  die absolute Temperatur,  $e$  die Elementarladung,  $z^*$  die effektive Ladung des Metallions als Maß für den Impulsaustausch,  $\varrho$  der spezifische elektrische Widerstand und  $j$  die elektrische Stromdichte [AN91, Ble76]. Die Diffusionskonstante  $D$  berechnet sich im Fall der kombinierten Korngrenzen- und Gitterdiffusion mit

$$D = D_v + \delta \cdot \frac{D_b}{d}, \quad (2.4)$$

wobei  $D_v$  die Diffusionskonstante für die Volumendiffusion und  $D_b$  die Diffusionskonstante für die Korngrenzendiffusion ist. Man muss dazu die Breite der Korngrenzen  $\delta$  und die mittlere Korngröße  $d$  berücksichtigen [AN91]. Die Aktivierungsenergien (siehe Black'sche Gleichung im Abschnitt 2.1.2) sind für die einzelnen Diffusionswege verschieden (Tabelle 2.1). Bei der Volumendiffusion muss die maximale Aktivierungsenergie aufgebracht werden, für die Korngrenzen- und Grenzflächendiffusion ist sie geringer. Dementsprechend ist die Diffusionskonstante für Volumendiffusion kleiner als die der anderen Diffusionsarten. An Korngrenzen und Grenzflächen tritt deshalb verstärkt EM auf.

Dabei ist es abhängig vom Werkstoff, welcher von beiden Diffusionswegen die geringere Aktivierungsenergie aufweist.

**Tabelle 2.1:** Aktivierungsenergien für verschiedene Diffusionspfade bei der Elektromigration in Aluminium und Kupfer

| Diffusionsprozess     | Aktivierungsenergie in eV |        |

|-----------------------|---------------------------|--------|

|                       | Aluminium                 | Kupfer |

| Gitterdiffusion       | 1,2                       | 2,3    |

| Korngrenzendiffusion  | 0,7                       | 1,2    |

| Grenzflächendiffusion | 0,8                       | 0,8    |

Wenn man sich zunächst auf das Innere einer Leitbahn konzentriert und Randeffekte vernachlässigt, kann man feststellen, dass speziell die Korngrenzen als Diffusionspfade dienen. Deshalb ist die Dichte und Richtung der Korngrenzen von Bedeutung für die EM und somit auch für die Zuverlässigkeit der Leitbahnen. Der Zusammenhang zwischen Korngröße und Elektromigrationsschäden wurde bereits Ende der 1960er Jahre festgestellt. Dabei konnte eine Häufung von Ausfällen beim Übergang zwischen verschiedenen Korngrößen gemessen werden [AR70]. Bei den untersuchten Aluminiumstreifen ließ sich die Schadensstelle in 66,7 % der Fälle dort lokalisieren, wo ein Übergang zwischen stark unterschiedlichen Korngrößen auftritt.

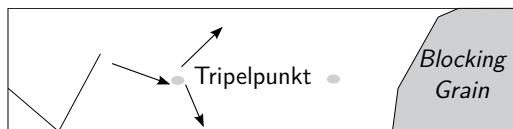

Polykristalline Strukturen mit einer geringeren Korngrenzdichte sind potentiell robuster gegenüber EM (siehe Abschnitt 5.2.1). Strukturen, die denen in der dritten und vierten Zeile im Bild 2.3 ähneln, besitzen weniger Korngrenzen, die in Stromflussrichtung ausgerichtet sind. Dadurch lässt sich die Korngrenzendiffusion teilweise unterbinden. Bei bambusähnlichen Strukturen (*Near Bamboo*) existieren einzelne Kristallite, die sich über die gesamte Breite der Leitbahn ausdehnen (*Blocking Grain*) und den Diffusionsfluss behindern. Dies führt jedoch dazu, dass gerade in der Nähe dieser Kristallite bevorzugt Schäden durch Voidbildung oder Materialansammlungen entstehen. Ursache für diese Schadensbilder ist eine Divergenz der Diffusion, die an diesen Blockaden oder Tripelpunkten entsteht. Es handelt sich dabei um Verzweigungen von Korngrenzen, die so angeordnet sind, dass sich von einer Richtung zwei Korngrenzen in einer einzigen fortsetzen (Bild 2.4).

**Bild 2.4:** Tripelpunkte und *Blocking Grains* bei bambusähnlichen Kornstrukturen

## 2.2.2 Barrieren bei Kupfermetallisierungen

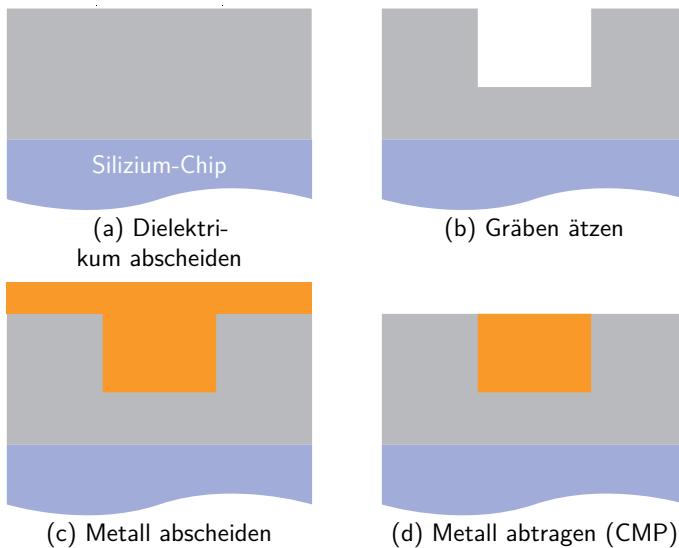

Bei Leitbahnen aus Kupfer lassen sich aufgrund der geringen Aktivierungsenergie für die Grenzfächendiffusion (siehe Tabelle 2.1) die Randeffekte nicht vernachlässigen. Kupfermetallisierungen werden überwiegend in der *Damascene*-Technologie hergestellt (Bild 2.5). Dabei erzeugt man durch Lithographie zuerst Vertiefungen (Gräben oder Kontaktlöcher) (b) im zuvor abgeschiedenen Dielektrikum (a). Kupfer wird dann vollflächig auf dem Wafer abgeschieden (c), sodass auch die Vertiefungen mit Kupfer gefüllt sind. Abschließend erfolgt ein Politurschritt (d), bei dem durch chemisch-mechanisches Polieren (*Chemical Mechanical Polishing (CMP)*) das Kupfer bis zur Oberkante der Vertiefungen wieder entfernt wird. Zurück bleiben die Leitbahnen und Vias in den Vertiefungen. Bei der Weiterentwicklung, der *Dual-Damascene*-Technologie lassen sich CMP-Schritte einsparen, indem eine Leitbahnebene und die darunterliegende Viaebene in einem gemeinsamen Schritt abgeschieden werden.

Das genannte Verfahren kann man jedoch nur mit weiteren technologischen Maßnahmen für Kupfer anwenden, denn Kupfer neigt zu starker Diffusion in benachbartes Silizium und Siliziumoxid bei hohen Temperaturen [UON<sup>+</sup>96]. Bei der Herstellung der Metallisierung und insbesondere beim Annealing zum Erzeugen von Bambusstrukturen (siehe Abschnitt 5.2) werden jedoch Temperaturen von bis zu 500 °C erreicht [CS11]. Die dadurch in Gang gesetzte Diffusion hat maßgeblich zwei negative Folgen. Einerseits bildet sich eine Kupfersilizidschicht, die eine geringe Leitfähigkeit aufweist; andererseits kann Kupfer die halbleitenden Eigenschaften des Siliziums zerstören. Für die Funktion von Schaltkreisen, die mit Kupfer-Mettallisierungen arbeiten, sind deshalb Barrieren zwischen Metall und Dielektrikum unerlässlich. Diese Barrieren dienen als Diffusionssperre für Kupfer und Silizium. Abhängig von ihrem Einsatzgebiet werden darüber hinaus sehr verschiedene Anforderungen an die Barrieren gestellt. Gemeinsam ist lediglich die Forderung nach guter Haftung auf Kupfer und

**Bild 2.5:** Vereinfachte Darstellung des *Damascene*-Verfahrens an einem Querschnitt einer Kupferleitbahn

dem Dielektrikum sowie thermischer und mechanischer Stabilität bei geringer Schichtdicke (wenige Nanometer).

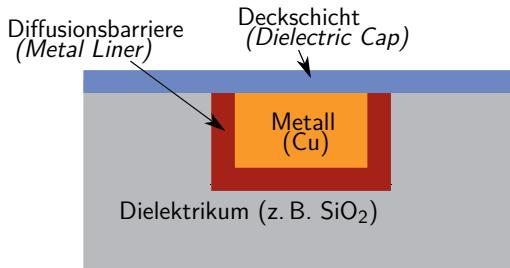

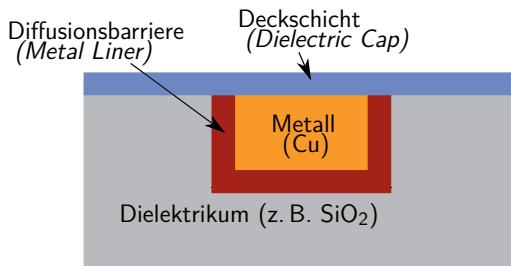

Der Begriff Barriere umfasst die metallische Diffusionsbarriere (*Metal Liner*) im Graben (*Trench*) und die, meist dielektrische, Deckschicht (*Dielectric Cap*). Zwischen Metall und Dielektrikum sowie zwischen Leitbahn und darüberliegendem Via befindet sich somit stets eine Barriere (Bild 2.6). Diese ist notwendig, um Diffusion insbesondere während der Herstellung zu verhindern [UON<sup>+</sup>96].

Die Diffusionsbarriere wird im geätzten Graben oder Kontaktloch im Dielektrikum abgeschieden, bevor die Kupferabscheidung stattfindet. Eine elektrische Leitfähigkeit ist hierbei erwünscht, da am Übergang zwischen Via und darunterliegender Metallebene eine solche Barriereschicht vorhanden ist. Außerdem kann die Diffusionsbarriere somit zum Stromfluss beitragen, was insbesondere bei Fehlern durch Voids eine Restleitfähigkeit sicherstellt.

Die Deckschicht befindet sich auf der Oberseite der Leitbahnen. Nach dem Abtrag im CMP-Schritt ist eine Barriere zum darüberliegenden Dielektrikum zu schaffen. Um hierbei auf eine weitere Strukturierung zu verzichten, bietet

**Bild 2.6:** Schematischer Querschnitt einer Kupferleitbahn mit den notwendigen Barrièreschichten

sich eine dielektrische Barriere an. Diese lässt sich vollflächig auf dem Wafer abscheiden, muss später lediglich beim Ätzen der Kontaktlöcher wieder geöffnet werden, um einen elektrischen Kontakt an den Vias herzustellen.

Eine elektrisch leitfähige Deckschicht müsste analog zur darunterliegenden Leitbahnebene lithografisch strukturiert werden oder sich als selbstorganisierender Prozess [CLJ08, LG09, VGH<sup>+</sup>12] ausschließlich auf der Kupferoberfläche anlagern und das freiliegende Dielektrikum aussparen (siehe Abschnitt 5.8.3).

Wie eingangs erwähnt hat die Barriere besondere Bedeutung für die EM, da sie den bei Kupfermetallisierungen besonders EM-empfindlichen Bereich der Grenzfläche bildet. Somit beeinflusst die Barriere maßgeblich die effektive Aktivierungsenergie der Kupferoberflächen. Es ist theoretisch möglich, durch die Wahl des Barriereförderwerkstoffes auch bei Kupfer die Aktivierungsenergie der Grenzflächendiffusion über das Niveau der Korngrenzendiffusion zu steigern und somit Grenzflächendiffusion zu verhindern. Man muss beachten, dass das Unterbinden eines Diffusionsmechanismus stets zur Folge hat, dass ein anderer Mechanismus dominiert, mit zum Teil sehr deutlichen Unterschieden im Schadensbild. Beim Wechsel von Aluminium zu Kupfer wurde zwar die Korngrenzendiffusion unterbunden, dafür ist jedoch die Grenzflächendiffusion stärker. Wenn nun die Grenzflächendiffusion durch geeignete Deck- und Barrièreschichten verhindert wird, tritt wieder die Korngrenzendiffusion stärker in den Vordergrund. Letztendlich ist es möglich, dass sogar die Gitterdiffusion als dominierender Prozess zum Tragen kommt, wenn alle anderen Mechanismen ausgeschaltet sind. Jede Änderung im dominierenden Diffusionsmechanismus

ändert die Ausfalleigenschaften und erhöht somit die Komplexität der Modellierung von Methoden zur EM-Vermeidung.

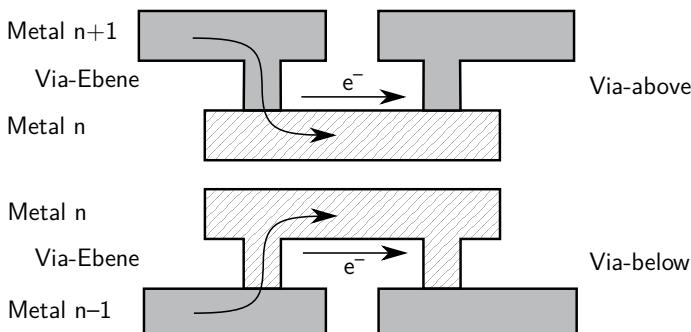

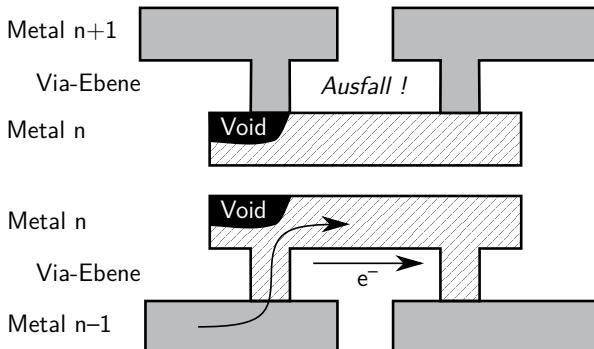

Die Unterscheidung zwischen Deckschicht und Diffusionsbarriere ist auch für die EM wichtig. Zwischen den bedeckten Kupferoberflächen bestehen entscheidende technologische Unterschiede. Beim *Dual-Damascene*-Verfahren [Gup09, Yoo08] wird eine zunächst vollflächig auf dem Wafer abgeschiedene Kupferschicht durch einen Politurschritt, das CMP-Verfahren, wieder abgetragen. Zurück bleibt nur das Kupfer in der Leitbahnebene und der darunterliegenden Via-Ebene. Dabei entstehen an der Oberfläche Defekte im Metall, die auch im weiteren Prozess nicht mehr behoben werden. Die hohe Defektdichte und Leerstellenkonzentration an der Oberseite der Leitbahnen verändern dort die Oberflächeneigenschaften und somit die Aktivierungsenergie. In Kombination mit einer schlechteren Haftung der dielektrischen Deckschicht neigt die Oberseite stärker zu Elektromigrationsschäden. Deshalb entstehen bevorzugt an der Oberseite einer Leitbahn Voids. Dies wirkt sich auf die zu verwendenden Werkstoffe (siehe Abschnitt 5.8) und auf bestimmte geometrische Leitbahnanordnungen (siehe Abschnitt 5.4) aus.

### 2.2.3 Einfluss durch mechanische Spannungen

Für mechanische Spannungen (mechanischen Stress) in Leitbahnen gibt es hauptsächlich drei Ursachen:

1. Die Abscheidung des Metalls findet bei hohen Temperaturen (ca. 500 °C) statt [CS11]. Durch die Abkühlung auf Umgebungstemperatur werden aufgrund der unterschiedlichen thermischen Ausdehnungskoeffizienten von Metall und Isolator mechanische Spannungen induziert.

2. Das Wachstum der Schichten bei der Metallabscheidung verläuft immer ungleichmäßig. Dadurch entstehen sich ebenfalls mechanische Spannungen in der Metallisierung. Laut [CS11] ist diese Ursache bedeutender als der erstgenannte Effekt. Dieser Sachverhalt lässt sich an Waferkrümmungsmessungen zeigen [CS11, BLK04].

3. EM erzeugt durch den Stofftransport und die daraus resultierende Umverteilung von Leerstellen im Metallgefüge mechanische Spannungen. Leer-

stellen benötigen weniger Volumen als ein Atom am selben Gitterplatz. Daher kann sich das Gitter entspannen, was zu einem lokal verringerten Stoffvolumen bzw. reduzierten Druckspannungen führt.

Mechanische Spannungen in Leitbahnen können sich je nach Werkstoffkombination und Herstellungsprozess unterschiedlich ausprägen. Ursache für Schäden sind dabei maßgeblich Zug- oder Druckspannungen in der Leitbahn, die jeweils einen Ausfallmechanismus begünstigen. Andere auftretende Spannungen lassen sich durch Gitterversetzungen abbauen.

In den Leitbahnen entsteht bei der Herstellung mechanischer Stress durch unterschiedliche thermische Ausdehnungskoeffizienten und hohe Temperaturen bei der Metallabscheidung. Die Temperatur des spannungsfreien Zustands, im Bereich um  $250\text{ }^{\circ}\text{C}$  [ZYB<sup>+</sup>04], liegt dabei in der Regel deutlich über der maximalen Betriebstemperatur. Da Kupfer mit  $16,5 \cdot 10^{-6}\text{ K}^{-1}$  [Gup09] einen wesentlich größeren Ausdehnungskoeffizienten als das umgebende Dielektrikum ( $\text{SiO}_2$ :  $0,5 \cdot 10^{-6}\text{ K}^{-1}$  [YW97]) besitzt, sind die Leitbahnen bereits unter normalen Betriebstemperaturen mechanischen (Zug-)Spannungen ausgesetzt. Unter Verwendung der Parameter

- $E_{\text{Cu}} = 117\text{ GPa}$ ,

- $E_{\text{SiO}_2} = 70\text{ GPa}$  und

- $\Delta T = 200\text{ K}$

ergibt sich bei der Annahme identischer Breiten von Metall und Dielektrikum bei eindimensionaler Berechnung mit der Näherung

$$\sigma = \frac{\alpha_{\text{SiO}_2} - \alpha_{\text{Cu}}}{E_{\text{SiO}_2}^{-1} + E_{\text{Cu}}^{-1}} \cdot \Delta T \quad (2.5)$$

eine Zugspannung von fast  $140\text{ MPa}$  in horizontaler Richtung senkrecht zur Länge der Leitbahn.

Zugspannungen fördern das Entstehen von Voids. Durch die Voidbildung bauen sich aufgrund der geänderten Topologie Zugspannungen ab, und es stellt sich ein lokal kräftefreier Zustand am Rand des Voids ein. Da hierbei der mechanische Kontakt zwischen Metall und Dielektrikum zerstört bzw. der leitfähige Querschnitt der Leitbahn verringert wird, ist die Entstehung von Voids möglichst zu vermeiden.

Die erlaubten Druckspannungen in Leitbahnen sind im Allgemeinen betragsmäßig höher als die erlaubten Zugspannungen. Sollte jedoch ein kritischer Betrag der Druckspannung überschritten werden, führt dies ebenfalls zum Abbau der Spannung. In diesem Fall bilden sich Extrusionen der Leitbahn, die sich in Form von *Dendriten*, *Whiskern* oder *Hillocks* in das benachbarte Dielektrikum ausbreiten. Dies ist vergleichbar mit dem Übergang von einer elastischen zu einer plastischen Verformung. Bevor Extrusionen entstehen, wird lediglich die Leerstellenkonzentration immer weiter reduziert. Dieser Vorgang ist teilweise reversibel. Extrusionen hingegen sind nicht mehr umkehrbar und führen zur Zerstörung des Schaltkreises.

## 2.2.4 Zusammenspiel der Migrationsarten

Neben der EM spielen weitere Formen der Diffusion in metallischen Verbindungsstrukturen eine Rolle für die Zuverlässigkeit. Temperaturgradienten erzeugen eine Thermomigration. Dabei steigern hohe Temperaturen die mittlere Geschwindigkeit der Atombewegungen. Dadurch überwiegt die Anzahl der Atome, die von Gebieten mit hoher Temperatur in Gebiete geringerer Temperatur diffundieren, gegenüber den Atomen mit umgekehrter Diffusionsrichtung. Dies führt zu einer Netto-Diffusion in Richtung des negativen Temperaturgradienten.

Stressmigration beschreibt eine Art der Diffusion, die zum Ausgleich mechanischer Spannungen führt. In Gebiete, in denen Zugspannungen wirken, fließt ein atomarer Nettofluss hinein, während die Metallionen aus Gebieten mit Druckspannung abfließen. Dies führt analog zur Thermomigration zu einer Diffusion in Richtung des negativen Gradienten der mechanischen (Druck-)Spannung. Es erfolgt somit ein Ausgleich der Leerstellenkonzentration entsprechend der mechanischen Spannung.

Die verschiedenen Arten der Migration lassen sich in ihren Auswirkungen nicht unabhängig voneinander betrachten. Die Stoffflüsse  $J_E$  von EM, Thermo-

migration  $J_T$  und Stressmigration  $J_S$  lassen sich folgendermaßen berechnen [WZDY03]:

$$\vec{J}_E = \frac{c}{kT} \cdot D_0 \cdot \exp\left(-\frac{E_a}{kT}\right) \cdot z^* e \varrho \vec{j}, \quad (2.6)$$

$$\vec{J}_T = -\frac{cQ}{kT^2} \cdot D_0 \cdot \exp\left(-\frac{E_a}{kT}\right) \cdot \text{grad } T, \quad (2.7)$$

$$\vec{J}_S = -\frac{c\Omega}{kT} \cdot D_0 \cdot \exp\left(-\frac{E_a}{kT}\right) \cdot \text{grad } \sigma. \quad (2.8)$$

Hierbei ist  $c$  die Konzentration der Atome,  $k$  die Boltzmannkonstante,  $T$  die absolute Temperatur,  $D_0$  die Diffusionskonstante bei Raumtemperatur,  $E_a$  die Aktivierungsenergie,  $z^*$  die effektive Ladung der Metallionen,  $e$  die Elementarladung,  $\varrho$  der spezifische elektrische Widerstand,  $j$  die elektrische Stromdichte,  $Q$  die transportierte Wärme,  $\Omega$  das atomare Volumen und  $\sigma$  die mechanische Spannung. Es entsteht stets ein Diffusionsfluss

$$\vec{J}_a = \vec{J}_E + \vec{J}_T + \vec{J}_S, \quad (2.9)$$

der sich aus dem Nettoeffekt der verschiedenen Triebkräfte ergibt. Grundsätzlich können die einzelnen Diffusionsflüsse in gleicher Richtung oder entgegengesetzt wirken. Nicht zu vernachlässigen ist außerdem die Kopplung der Mechanismen, also die Rückwirkung der Diffusion auf die Ursachen des Stofftransports. Die Längeneffekte entstehen durch eine solche negative Rückkopplung zwischen EM und Stressmigration.

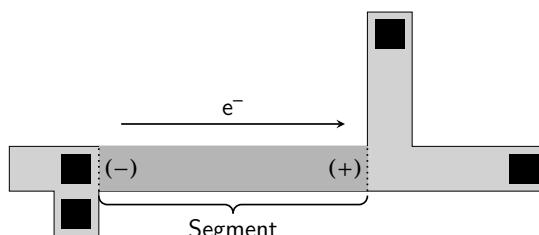

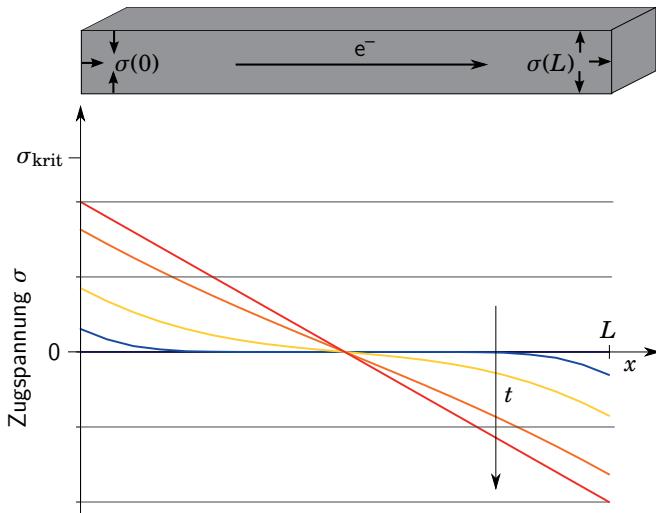

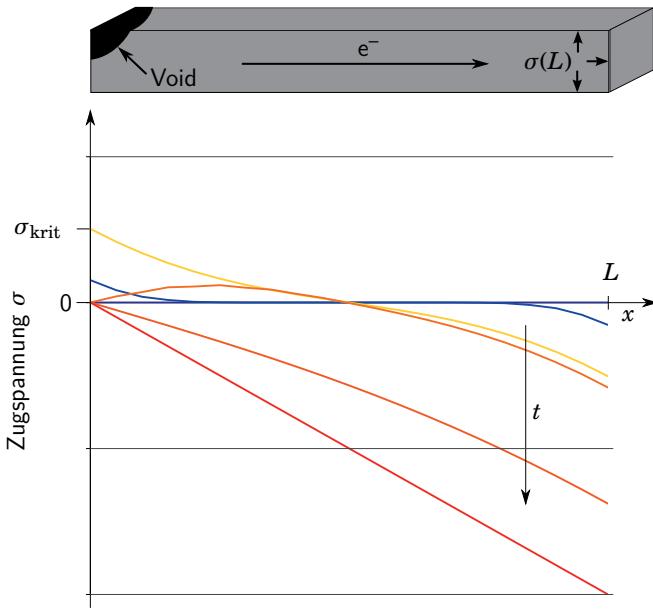

Der resultierende Diffusionsstrom wird eindimensional durch

$$J_a = \frac{Dc}{kT} \cdot \varrho j z^* e + \frac{Dc}{kT} \cdot \Omega \cdot \frac{\partial \sigma}{\partial x} \quad (2.10)$$

beschrieben [Tho08]. Dabei ist  $J_a$  der atomare Fluss,  $D$  die Diffusionskonstante von Kupfer mit

$$D = D_0 \cdot \exp\left(-\frac{E_a}{kT}\right), \quad (2.11)$$

$c$  die Konzentration der Kupferatome,  $j$  die Stromdichte,  $z^*$  die effektive Ladung von Kupfer,  $e$  die Elementarladung,  $k$  die Boltzmannkonstante,  $T$  die Temperatur,  $\Omega$  das Atomvolumen von Kupfer,  $\sigma$  die mechanische Spannung und  $x$  die Koordinate längs des Segments mit  $x = 0$  an der Kathode. Um Elektromigrationserscheinungen zu verhindern, muss der Nettodiffusionsstrom zu Null

reduziert werden. Das heißt beispielsweise, EM und Stressmigration heben sich gegenseitig auf.

## 2.2.5 Frequenzabhängigkeit der EM

Wenn man im Betrieb einer Leitbahn die Stromrichtung umkehrt, invertiert sich ebenfalls die Diffusionsrichtung der EM. Dadurch können entstandene Schäden durch EM teilweise wieder behoben werden. Dieser Effekt wird Selbstheilung genannt, da er durch die EM selbst bewirkt wird. Ob die Selbstheilung entstehende Schäden effektiv beheben kann und somit zur Steigerung der Lebensdauer einer Leitbahn beiträgt, hängt von der Größe der Schäden und Gefügeveränderungen vor der Richtungsumkehr des Stroms ab. Deshalb wirkt hier die Frequenz als entscheidender Parameter, da sie zusammen mit dem Tastverhältnis die Dauer der einseitigen Strombelastung vorgibt.

Bei hohen Frequenzen wird pro Halbwelle nur wenig Metall bewegt. Es entstehen also nur geringe Veränderungen an der Gefügestruktur. Dadurch entspricht der Stromfluss in der zweiten Halbwelle ungefähr dem Spiegelbild der ersten Halbwelle, sodass sich die Veränderungen mit hoher Wahrscheinlichkeit umkehren lassen. Dadurch verzögert sich der Zeitpunkt, an dem erste Schäden in Form von Fehlstellen und Voids auftreten. Messungen bei verschiedenen Frequenzen konnten zeigen, dass sich eine alternierende Widerstandsänderung (Anteil der Selbstheilung) mit einem langsam steigenden Widerstand überlagert [TCH93]. Somit ist die teilweise Selbstheilung nachgewiesen.

Der Grad der Selbstheilung lässt sich mit den Diffusionsflüssen  $J$  durch

$$J_{\text{netto}} = J_{\text{hin}} - J_{\text{rück}} = J_{\text{hin}} \cdot (1 - \gamma) \quad (2.12)$$

ausdrücken [TCH93, TCCH96], wobei  $\gamma$  der Selbstheilungskoeffizient ist. Dieser Koeffizient wird bestimmt durch den Tastgrad  $r$  (*Duty Ratio / Duty Cycle*) des Stroms sowie andere Faktoren, die den Grad der Selbstheilung beeinflussen, wie beispielsweise die Frequenz.

In [DFN06] wird der Selbstheilungskoeffizient über

$$MTTF_{\text{AC}} = \frac{A}{(r \cdot j^+ - \gamma \cdot (1 - r) \cdot j^-)^n} \cdot \exp\left(\frac{E_a}{kT}\right) \quad (2.13)$$

definiert (vgl. Gleichung (2.1)). Experimentell wird in derselben Veröffentlichung der Selbstheilungskoeffizient empirisch durch

$$\gamma = \frac{r \cdot \frac{j^+}{j_{DC}} - s \cdot \frac{MTTF_{DC}}{MTTF_{AC}}}{(1-r) \cdot \frac{j^-}{j_{DC}}} \quad (2.14)$$

bestimmt. Dabei ist  $j^+$  die Stromdichte der positiven Halbwelle und  $j^-$  die der negativen. Der Skalierungsfaktor  $s$  ist iterativ zu ermitteln.

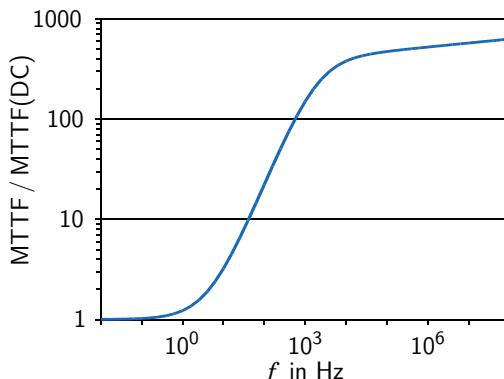

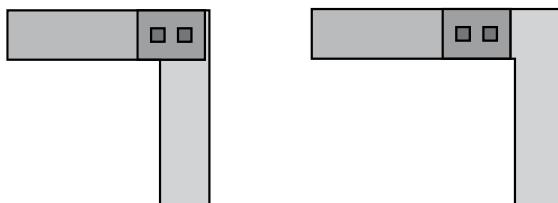

Nach Tao et al. [TCH93] erfolgt eine Steigerung der Lebensdauer (MTTF) gegenüber geringen Frequenzen bzw. Gleichstrom um den Faktor 500 bei Frequenzen von 10 bis  $10^4$  Hz (Bild 2.7). Dabei wurde mit rechteckförmigen Stromsignalen gearbeitet, bei Frequenzen von einigen mHz bis 200 MHz. Der Grund für die auch bei hohen Frequenzen begrenzte Lebensdauer ist das Zusammenspiel von EM und Thermomigration, das die Leitbahnen zerstört. Es ist zu erkennen, dass die Änderung der Lebensdauer in einem Frequenzbereich erfolgt, der für heutige digitale Schaltungen eine sehr geringe Bedeutung hat. Lediglich Teilschaltungen, die der Interaktion mit der Umwelt bzw. mit dem Menschen dienen, verarbeiten Signale in diesem „niedrigen“ Frequenzbereich (Tabelle 2.2).

Sonstige Signalfrequenzen sind in der Regel wesentlich höher (Mega- oder Gigahertz-Bereich), während die Ströme in Versorgungsleitungen aus einem starken Gleichanteil mit überlagerten Schwankungen mit sehr geringen Frequenzen bestehen. Daher ist eine hohe Frequenz allein nicht zur Verhinde-

Bild 2.7: Frequenzabhängigkeit der mittleren Lebensdauer nach [TCH93]

**Tabelle 2.2:** Beispiele für technisch relevante Frequenzen

| Beispiel                                                 | Frequenz  |

|----------------------------------------------------------|-----------|

| Schalten der Hintergrundbeleuchtung eines Bildschirms    | 10 mHz    |

| Bildwiederholrate eines PC-Monitors                      | 60 Hz     |

| Abtastfrequenz für Audiosignale                          | 44 kHz    |

| Trägerfrequenz für Radio-Frequency Identification (RFID) | 13,56 MHz |

| Taktfrequenz eines Prozessors                            | 3 GHz     |

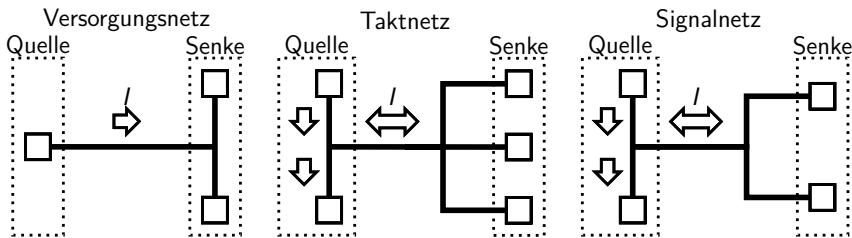

rung von Schäden geeignet. Die Frequenzabhängigkeit zeigt jedoch, dass man zwischen Signalleitungen und Versorgungsleitungen bei der Analyse von EM unterscheiden muss.

In [DFN06] wird ein empirisches Modell für die Heilung von Schäden entworfen, siehe Gleichung (2.13). Shono et al. [SKSY90] modellieren ebenfalls den Hin- und Rücktransport von Metall aufgrund der Stromrichtungsumkehr. Dabei gehen sie davon aus, dass die Ladungsmenge in beiden Richtungen identisch ist (also kein Gleichanteil), der Strom jedoch zeitlich asymmetrisch verläuft. In einer Richtung gibt es lange Strompulse geringer Amplitude, in der Gegenrichtung entsprechend kürzere mit großer Amplitude. Folglich ergibt sich wegen dem nichtlinearen Zusammenhang zur Stromdichte ein asymmetrischer Stofftransport mit einem Netto-Fluss in eine Richtung. Die minimale Lebensdauer wird bei diesem Modell bei einem Tastgrad, also dem Verhältnis zwischen Länge des positiven Pulses und Periodendauer, von ungefähr 0,4 erreicht. In [JJ11] wird die signalformabhängige Zuverlässigkeit beschrieben. Li et al. [LWW<sup>+</sup>99] untersuchen anhand numerischer Berechnungen die Lebensdauer in Abhängigkeit von der Frequenz.

Die Veröffentlichung [SHK<sup>+</sup>11] stellt eine Verknüpfung zu den Via-above- und Via-below-Anordnungen (siehe Abschnitt 5.4) her, indem die Auswirkungen von Gleich- und Wechselstrom auf solche Strukturen analysiert werden.

Bei sehr hohen Frequenzen findet eine Stromverdrängung aus dem stromdurchflossenen Leiter statt. Dann steigt die Stromdichte in den äußeren Bereichen des Leiters. Das Innere trägt nur noch in geringem Maß zum Stromtransport bei. Diesen bezeichnet man als Skin-Effekt. Als Maß für die Stromverdrängung wird meist die Eindringtiefe

$$\delta = \sqrt{\frac{2\rho}{\omega \cdot \mu}} \quad (2.15)$$

angegeben, wobei  $\rho$  der spezifische elektrische Widerstand und  $\mu$  die Permeabilität des Leiterwerkstoffs ist. Die Variable  $\omega$  bezeichnet die Kreisfrequenz mit  $\omega = 2\pi f$ . Die Stromdichte nimmt näherungsweise nach einer Exponentialfunktion mit den Variablen  $j_S$  als äquivalente Randstromdichte und  $d$  als Entfernung von der Oberfläche ab:

$$j \approx j_S \cdot \exp\left(-\frac{d}{\delta}\right). \quad (2.16)$$

Eine bessere Näherung für den Verlauf der Stromdichte in einem langen zylindrischen stromdurchflossenen Leiter [KMR13] lässt sich analytisch beschreiben durch

$$j_{\text{eff}}(r) = \frac{I}{2\pi r_0} \cdot \sqrt{\omega\kappa\mu} \cdot \sqrt{\frac{r_0}{r}} \cdot \exp\left[-\sqrt{\omega\kappa\mu} \cdot (r_0 - r)\right]. \quad (2.17)$$

Dabei bezeichnet  $\kappa = 1/\rho$  die elektrische Leitfähigkeit und  $r_0$  den Querschnittsradius des Leiters. Für Leiter mit rechteckigem Querschnitt ist die analytische Herleitung nicht ohne weiteres möglich. Das Modell eines zylindrischen Leiters genügt jedoch hier, um die Größenordnung abzuschätzen.

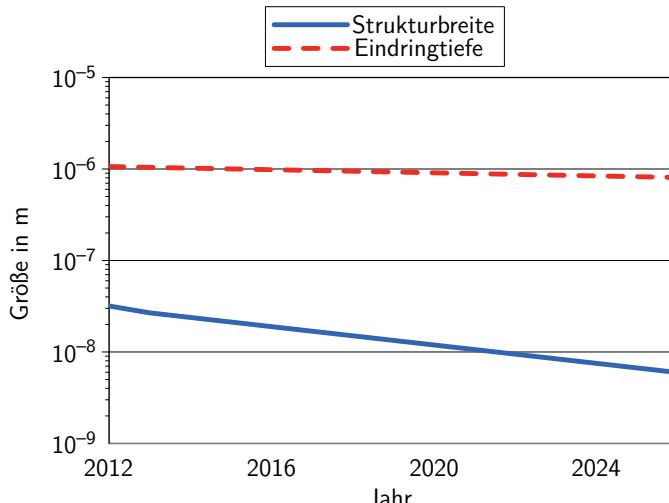

Für Kupfer liegt die Eindringtiefe bei 50 Hz noch bei ca. 9,4 mm und ist proportional zu  $f^{-2}$ . In [WY02] wird für eine Leitbahn quadratischen Querschnitts der Abmessungen Breite  $W$  und Höhe  $t$  mit  $W = t = 0,45 \mu\text{m}$  eine kritische Frequenz von 90 GHz für den Skineffekt bestimmt. Bei analoger Berechnung liegt für heutige 22 nm-Strukturen die kritische Frequenz mit ca. 35 THz deutlich höher.

Verglichen mit der derzeitigen Halbleiterentwicklung, bezogen auf Leitbahnbreiten und Taktfrequenzen, sind Probleme durch den Skineffekt in digitalen Schaltungen vorerst nicht zu erwarten. Die Leitbahnamessungen sinken wesentlich schneller als die frequenzabhängige Eindringtiefe (Bild 2.8). Jedoch kann der Effekt bereits bei aktuellen Frequenzen die hochfrequenten Signaleanteile und somit die Taktflanken stören. Hinzu kommt, dass der Skineffekt bei geringerer Leitfähigkeit abnimmt und somit durch die steigende Einflussnahme von Randeffekten an den Leitbahnen geschwächt wird.

**Bild 2.8:** Vergleich zwischen minimalen Strukturabmessungen und Eindringtiefe beim Skineffekt; Daten aus [ITR12]; in den unteren Metalllagen mit Strukturgrößen kleiner als 100 nm kann demnach der Skineffekt vernachlässigt werden

## 2.3 Berücksichtigung von EM im Layoutentwurf

### 2.3.1 Einordnung in den Layoutentwurf

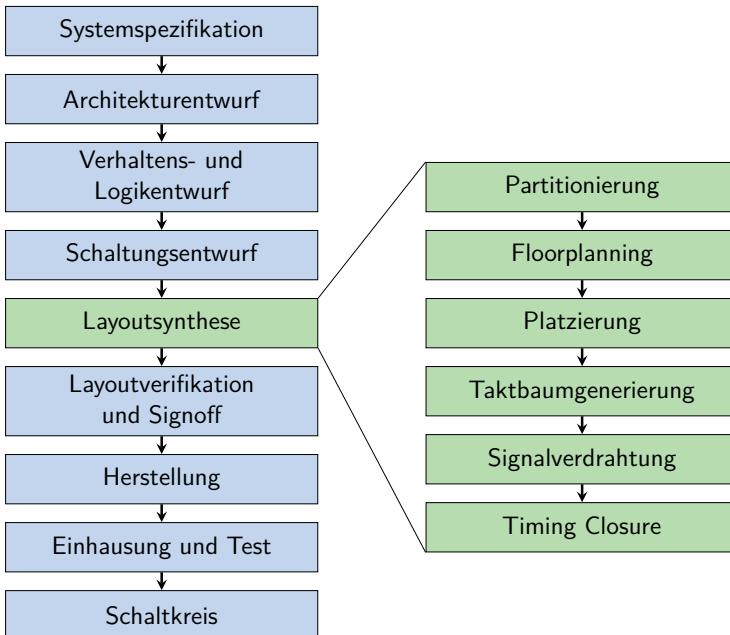

Der *Layoutentwurf* elektronischer Schaltungen umfasst das Erstellen (Synthese) und die Verifikation (Analyse) der geometrischen Anordnung der Zellen oder Bauelemente und ihrer Verbindungen [Lie06b]. Unter Verifikation versteht man die Prüfung des entworfenen Layouts auf Einhaltung aller Randbedingungen. Der Entwurf erfolgt schrittweise, sodass über mehrere prüfbare Zwischenergebnisse ein immer konkreteres Layout erreicht wird. Speziell bei digitalen Schaltungen erfolgt eine Reihe von Iterationen von Synthese- und Verifikationsschritten bis zum fertiggestellten Layout. Diese Schrittfolge läuft dabei weitgehend rechnergestützt und automatisiert ab. Zur Veranschaulichung sind die wichtigsten Entwurfsschritte in Bild 2.9 dargestellt.

Die Berücksichtigung von Elektromigration kann in verschiedenen Entwurfschritten erfolgen. Eine Möglichkeit ist die Verifikation in Hinblick auf die EM-Robustheit durch rechnergestützte Analyse der Schaltung bzw. des Layouts.

**Bild 2.9:** Wesentliche Schritte des Entwurfsflusses beim digitalen Schaltkreisentwurf und Ablauf der Layoutsynthese, nach [KLMH11].

Vorrausschauend ist die EM-Berücksichtigung bereits während des Entwurfs durch stromabhängige Verdrahtung und Anpassung der Leitbahnbreiten möglich.

Bei der Verifikation erfolgt je nach Entwurfsstadium eine Prüfung der auftretenden lokalen Stromdichte oder des Stroms. Im Layout kann die Stromdichte in Abhängigkeit von geometrischen Eigenschaften der Verdrahtung bestimmt und mit einer maximal zulässigen Stromdichte verglichen werden. Überschreitungen sind dann zu signalisieren und durch entsprechende Änderungen am Layout zu beheben.

Zur EM-Berücksichtigung während der Layouterstellung sind Platzierung und/oder Verdrahtung stromabhängig durchzuführen. Dabei gelten die aus der Schaltungssimulation gewonnenen Ströme und die zulässigen Stromdichten als Randbedingung. Unter diesen Voraussetzungen platziert man die Funktionsblöcke so, dass möglichst geringe Ströme auftreten und erzeugt Leitbahnen mit einer

Breite, die diesen Strömen angepasst ist. Bei der Verdrahtung ist neben der Breite der Leitbahnen auch der Verdrahtungsweg, insbesondere bei Netzen mit mehr als zwei Knoten, von Bedeutung. Dabei ist es möglich, durch günstiges Setzen von Steiner-Punkten, den Betrag des Stroms in den einzelnen Segmenten zu senken [LJ03, LKL<sup>+</sup>12]. Steiner-Punkte oder Steinerknoten sind Verzweigungen eines Netzes, also zusätzliche Knoten im Verdrahtungsnetz ohne direkten Transistoranschluss.

Generell ist zwischen Analog- und Digitalentwurf zu unterscheiden. Analoge Schaltungen sind im Allgemeinen weniger komplex, dafür aber von Hand individuell zu entwerfen. Dabei muss man zahlreiche funktionsrelevante Randbedingungen beachten, die die Entwurfsautomatisierung bzw. Analogsynthese bisher verhindern.

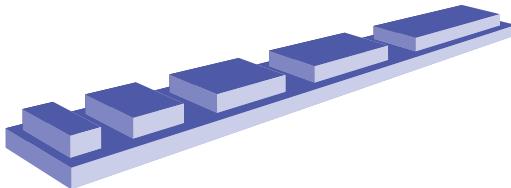

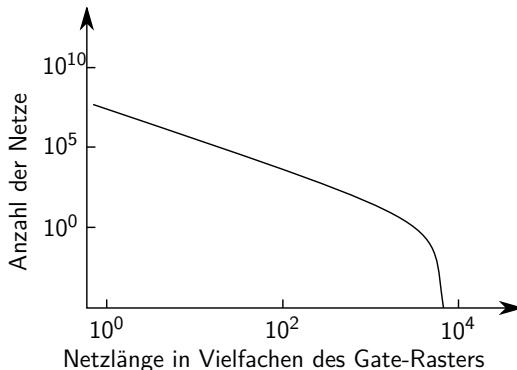

### 2.3.2 Besonderheiten des digitalen Layoutentwurfs

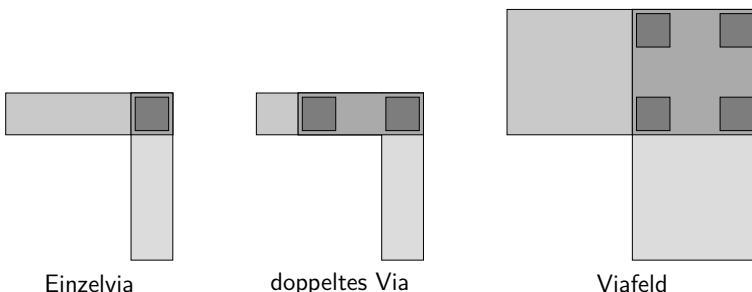

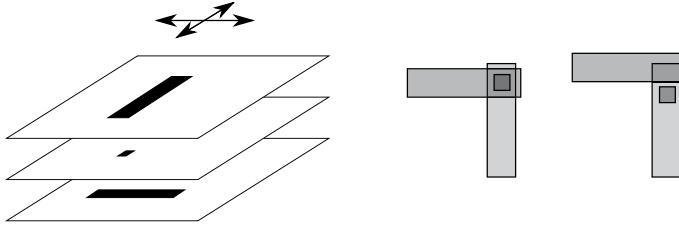

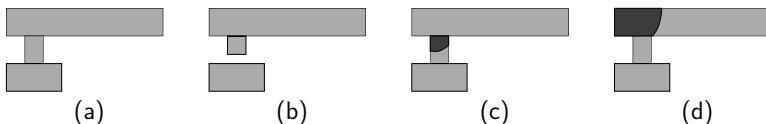

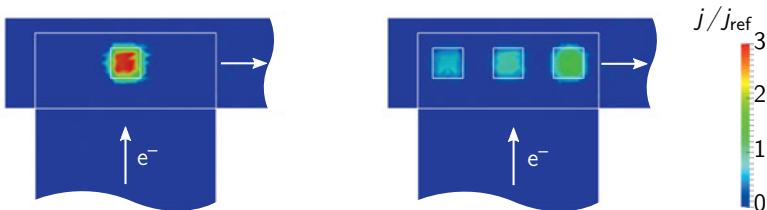

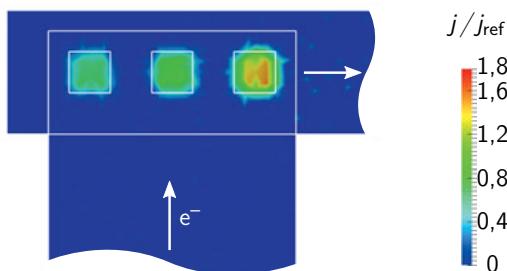

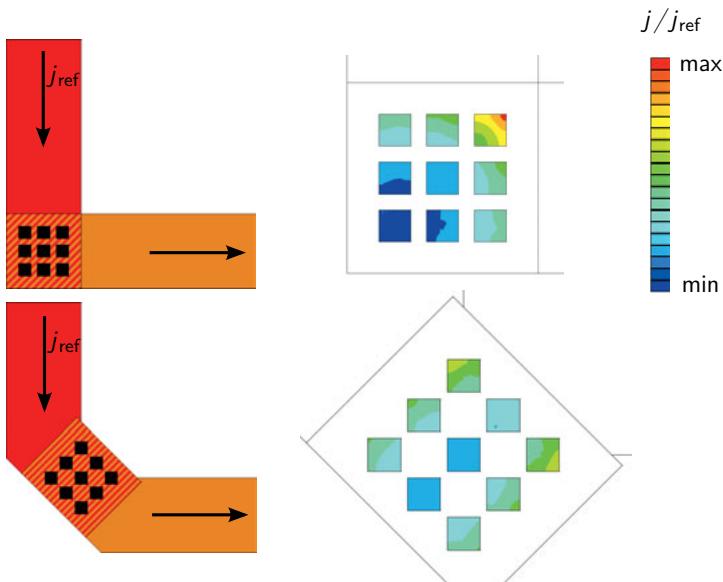

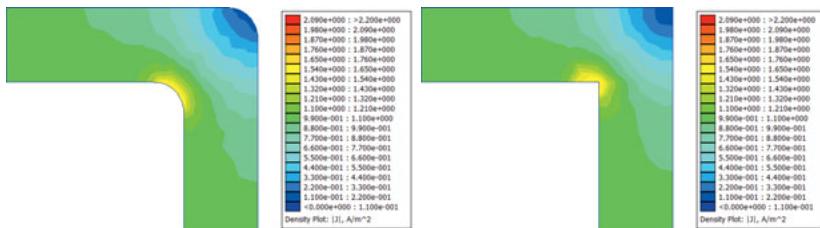

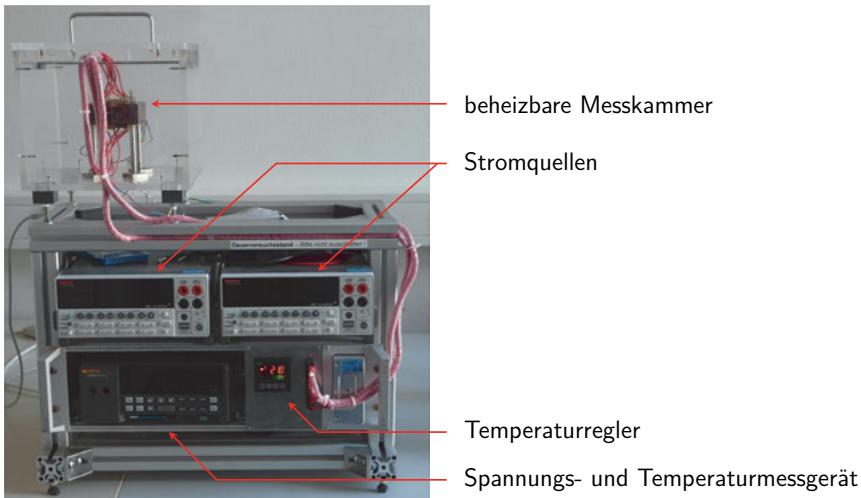

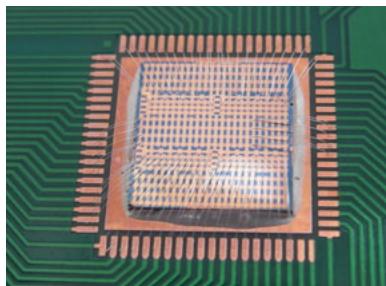

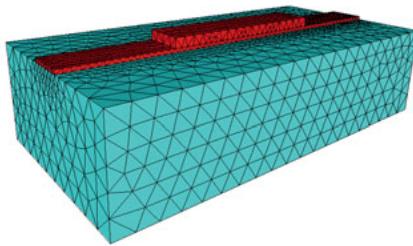

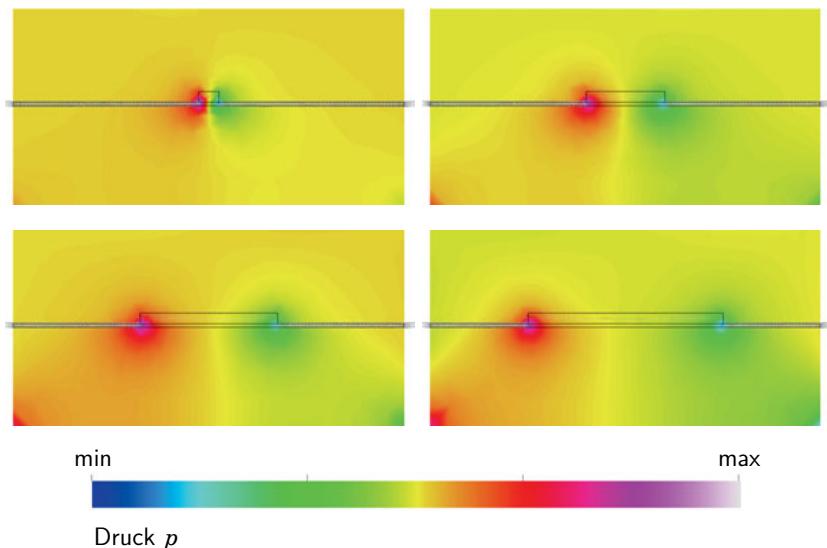

Die Besonderheit digitaler Schaltungen besteht darin, dass statt analoger Werte und Funktionen digitale Werte verarbeitet werden. Digitale Werte sind zeit- und wertdiskret. Daraus resultiert eine geringere Empfindlichkeit gegenüber Störungen. Des Weiteren sind weniger Randbedingungen im Entwurf erforderlich, um die Funktion sicherzustellen. Deshalb lassen sich mit relativ einfachen Synthesealgorithmen Schaltungen generieren. Dies ist mittels der *Logiksynthese* (ersetzt den Schaltungsentwurf in Bild 2.9) möglich. Durch die automatische Generierung kann man wesentlich komplexere Schaltungen entwerfen als im Handentwurf. Deshalb können heutige digitale Schaltkreise sehr komplex sein. Sie besitzen eine große Anzahl von Bauelementen und elektrischen Verbindungen (Netzen) und lassen sich deshalb nur mit Unterstützung von Computern ökonomisch erstellen, verifizieren und analysieren. Durch Strukturverkleinerungen nimmt die Komplexität im Laufe der Zeit und mit der weiteren Entwicklung stetig zu.