# Fortschritt-Berichte VDI

VDI

Reihe 21

Elektrotechnik

Nr. 419

Dipl.-Ing. Christian Bödeker,

Bremen

## Extrinsische und intrinsische Beeinflussungen des Verhaltens von Siliziumkarbid- Leistungshalbleiter- bauelementen

Berichte des Instituts für elektrische

Antriebe, Leistungselektronik und

Bauelemente der Universität Bremen

# Extrinsische und intrinsische Beeinflussungen des Verhaltens von Siliziumkarbid-Leistungshalbleiterbauelementen

Vom Fachbereich für Physik und Elektrotechnik

der Universität Bremen

zur Erlangung des akademischen Grades eines

**Doktor-Ingenieur (Dr.-Ing.)**

genehmigte Dissertation

von

Dipl.-Ing. Christian Bödeker

aus Bremen

Referent: Prof. Dr.-Ing. Nando Kaminski

Korreferent: Prof. Dr.-Ing. Josef Lutz

Eingereicht am: 09.03.2018

Tag des Promotionskolloquiums: 18.09.2018

# Fortschritt-Berichte VDI

Reihe 21

Elektrotechnik

Dipl.-Ing. Christian Bödeker,

Bremen

Nr. 419

Extrinsische und

intrinsische

Beeinflussungen des

Verhaltens von

Siliziumkarbid-

Leistungshalbleiter-

bauelementen

Berichte des Instituts für elektrische

Antriebe, Leistungselektronik und

Bauelemente der Universität Bremen

Bödeker, Christian

## **Extrinsische und intrinsische Beeinflussungen des Verhaltens von Siliziumkarbid-Leistungshalbleiterbauelementen**

Fortschr.-Ber. VDI Reihe 21 Nr. 419. Düsseldorf: VDI Verlag 2019.

184 Seiten, 179 Bilder, 18 Tabellen.

ISBN 978-3-18-341921-0, ISSN 0178-9481,

€ 67,00/VDI-Mitgliederpreis € 60,30.

**Für die Dokumentation:** Siliziumkarbid – parasitäre Elemente – Streuinduktivität – Messwiderstand – thermische Stabilität – statisches und dynamisches Verhalten – Halbleitergehäuse – Kelvin-Source-Anschluss – Kurzschlussverhalten – Überspannungsschutz

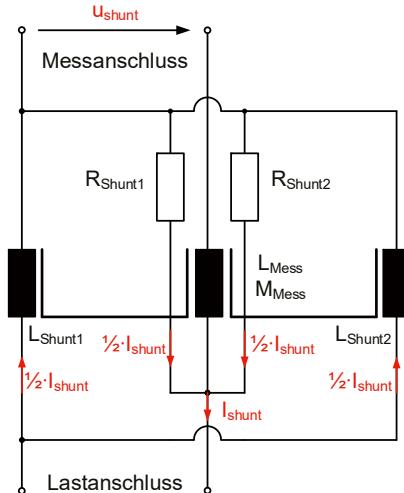

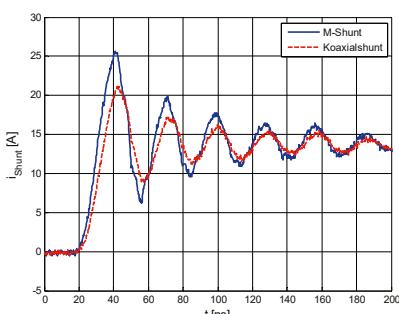

Die vorliegende Arbeit beschäftigt sich mit dem Verhalten von Halbleitern aus Siliziumkarbid (SiC). Zunächst werden die Auswirkungen par. Elemente betrachtet. Es wird u.a. der planare M-Shunt untersucht. Die Charakterisierung der Halbleiter wird mit stat. und dyn. Messmethoden durchgeführt. Der Sperrbetrieb der Dioden wird im Hinblick auf therm. Stabilität untersucht und bei der dyn. Charakterisierung werden die Überspannung sowie die Ladung bestimmt. Bei den stat. Messungen der Transistoren wird das Verhalten hinsichtlich verschiedener Transistorarten sowie herstellerbedingter Unterschiede aufgezeigt. Die dyn. Vermessung der Transistoren umfasst eine Analyse des Einflusses der Ansteuerparameter, der Gehäuse, der Sperrsichtstemperatur und unterschiedlicher Dioden auf das Schaltverhalten. Des Weiteren werden die Zerstörungsgrenzen von SiC-MOSFETs und die Anwendbarkeit von Überspannungsschutzbeschaltungen auf SiC-MOSFETs analysiert.

### **Bibliographische Information der Deutschen Bibliothek**

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliographie; detaillierte bibliographische Daten sind im Internet unter [www.dnb.de](http://www.dnb.de) abrufbar.

### **Bibliographic information published by the Deutsche Bibliothek**

(German National Library)

The Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliographie (German National Bibliography); detailed bibliographic data is available via Internet at [www.dnb.de](http://www.dnb.de).

Dissertation Universität Bremen

© VDI Verlag GmbH · Düsseldorf 2019

Alle Rechte, auch das des auszugsweisen Nachdruckes, der auszugsweisen oder vollständigen Wiedergabe (Fotokopie, Mikrokopie), der Speicherung in Datenverarbeitungsanlagen, im Internet und das der Übersetzung, vorbehalten.

Als Manuskript gedruckt. Printed in Germany.

ISSN 0178-9481

ISBN 978-3-18-341921-0

---

Verlags-Innentitel (gestaltet vom Verlag)

Impressumseite (gestaltet vom Verlag)

## Vorwort

Die Grundlage für die vorliegende Arbeit wurde im Rahmen meiner Anstellung am Institut für elektrische Antriebe, Leistungselektronik und Bauelemente (IALB) der Universität Bremen im Zeitraum zwischen September 2010 und November 2017 gelegt. Die Tätigkeit am IALB hat mir die Gelegenheit gegeben, Forschungsergebnisse zu erzielen, welche in eine Vielzahl an Veröffentlichungen und darüber hinaus auch in diese Arbeit eingegangen sind. Hierbei hat die Arbeit unter anderem Unterstützung vom European Center for Power Electronics e. V. (ECPE) im Zusammenhang mit dem Projekt „Current Measurement with Low-inductive Planar Shunts“ erfahren, das im Rahmen des „ECPE Joint Research Programme“ gefördert wurde. Einige der Veröffentlichungen sind durch Kooperationen mit Industriepartnern beziehungsweise der Unterstützung von Firmen entstanden. Hierbei ist im Speziellen Dr. Jeffrey B. Cassidy, Edgar Ayerbe und Cam Pham von Wolfspeed, Dr. Ranbir Singh von GeneSiC, Dr. Martin Domeij von ON Semiconductor sowie der Firma Isabellenhütte Heusler ein Dank für die Versorgung mit Materialien und auch Informationen auszusprechen.

Bei meinem Doktorvater Herrn Prof. Dr.-Ing. Nando Kaminski sowie Herrn Prof. Dr.-Ing. Josef Lutz möchte ich mich für die Übernahme der Gutachten zu dieser Arbeit bedanken. Des Weiteren gilt mein Dank Herrn Prof. Dr.-Ing. Nando Kaminski, Herrn Prof. Dr. phil. nat. Dieter Silber und natürlich allen Kolleginnen und Kollegen beider Arbeitsgruppen des IALBs für die vielen hilfreichen und wertvollen Diskussionen. Insbesondere sind diesbezüglich Melanie Adelmund, Alexander Würfel, Michael Hanf, Matthias Joost und Jacek Borecki hervorzuheben. Ferner sei Dr.-Ing. Tobias Appel (ehemals Universität Rostock) für einige hilfreiche Hinweise gedankt.

Die zahlreichen betreuten studentischen Arbeitsvorhaben an der Universität Bremen haben selbstverständlich auch zur vorliegenden Arbeit beigetragen. Hierfür danke ich allen von mir betreuten Studentinnen und Studenten recht herzlich. Ebenfalls möchte ich mich bei allen Studenten bedanken, die im Rahmen einer Anstellung als Hilfskraft beigetragen haben.

Ein weiterer großer Dank gilt Elke Krüger, Melanie Adelmund, Michael Hanf und Alexander Würfel für die Durchsicht der Rohfassung der Arbeit auf Fehler.

Zu guter Letzt möchte ich meinen Eltern ganz herzlich für die jahrelange Unterstützung während des Studiums und der anschließenden Zeit der Promotion danken.

# Inhalt

|                                                                                  |      |

|----------------------------------------------------------------------------------|------|

| Vorwort.....                                                                     | III  |

| Inhalt.....                                                                      | V    |

| Formelzeichen und Abkürzungen.....                                               | VII  |

| Kurzfassung.....                                                                 | XIII |

| Abstract .....                                                                   | XIV  |

| 1 Einleitung.....                                                                | 1    |

| 2 Grundlagen der Siliziumkarbid-Bauelemente .....                                | 3    |

| 2.1 Materialeigenschaften .....                                                  | 3    |

| 2.2 Siliziumkarbid-Bauelemente .....                                             | 5    |

| 2.2.1 pin-Diode.....                                                             | 5    |

| 2.2.2 Schottky-Diode .....                                                       | 6    |

| 2.2.3 Bipolartransistor (BJT).....                                               | 8    |

| 2.2.4 Sperrsichtfeldeffektransistor (JFET) .....                                 | 11   |

| 2.2.5 Metall-Oxid-Halbleiter-Feldeffektransistor (MOSFET) .....                  | 14   |

| 2.3 Parasitäre Elemente.....                                                     | 17   |

| 3 Messtechnik.....                                                               | 21   |

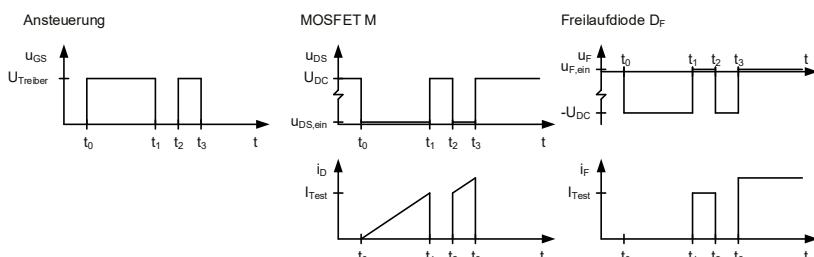

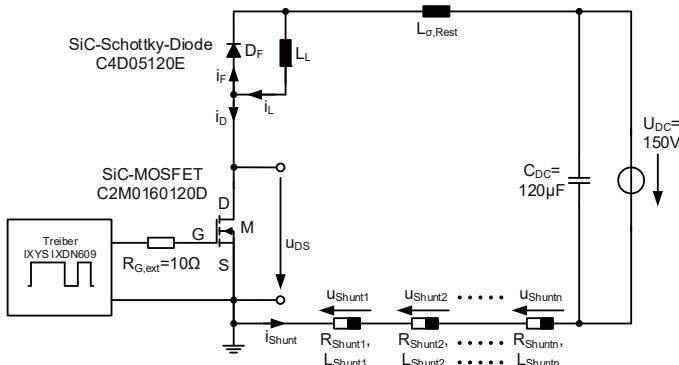

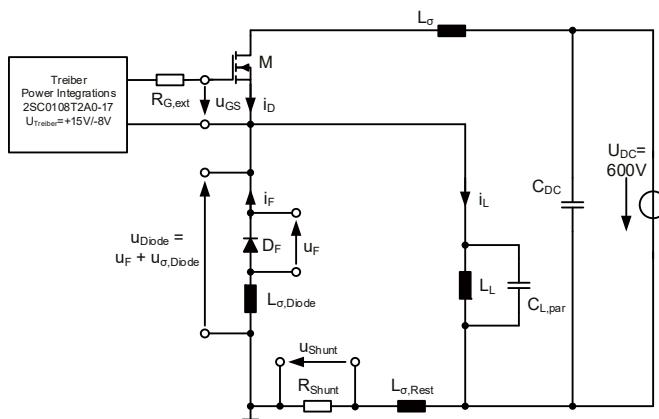

| 3.1 Schaltversuche .....                                                         | 21   |

| 3.1.1 Doppelpulsversuch.....                                                     | 22   |

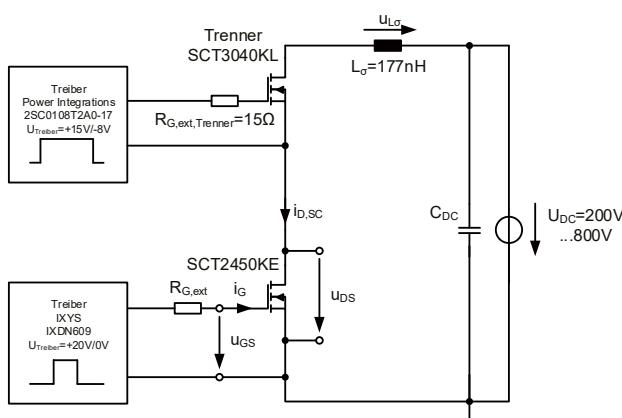

| 3.1.2 Kurzschlussversuch.....                                                    | 24   |

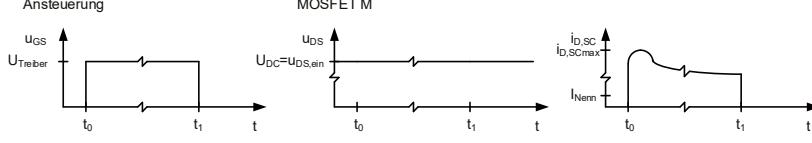

| 3.1.3 Messplatzkonzept .....                                                     | 25   |

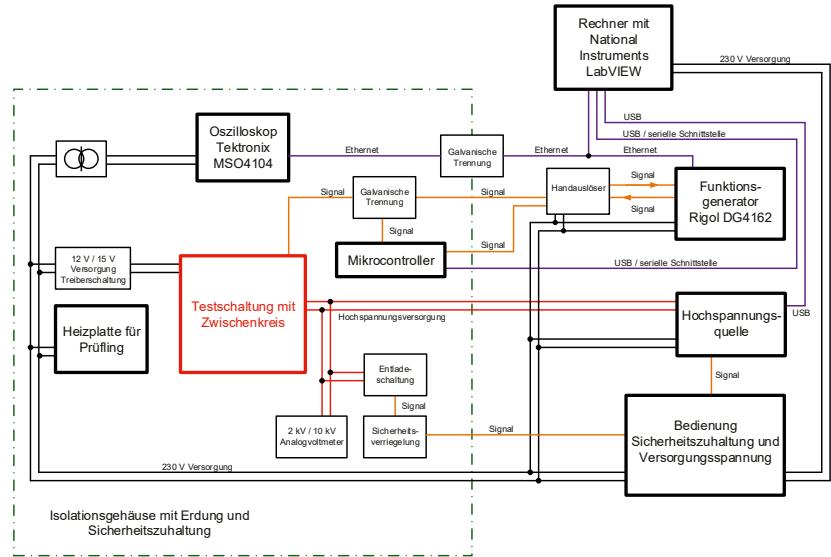

| 3.1.4 Schaltverläufe und deren Auswertung.....                                   | 27   |

| 3.2 Strommessung über einen Widerstand.....                                      | 31   |

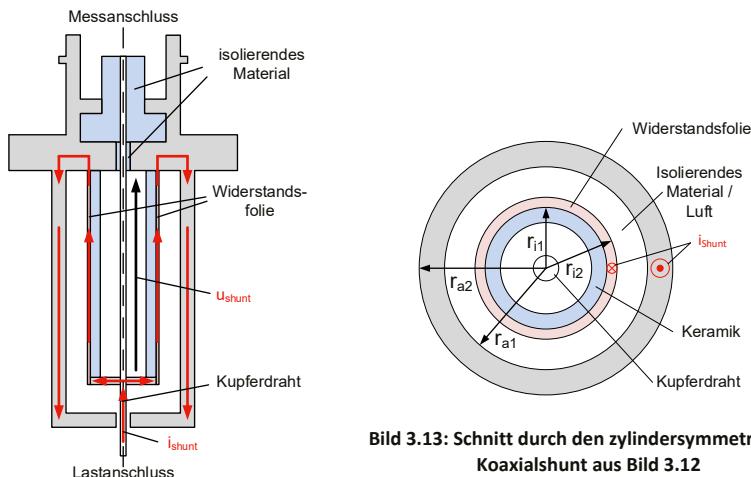

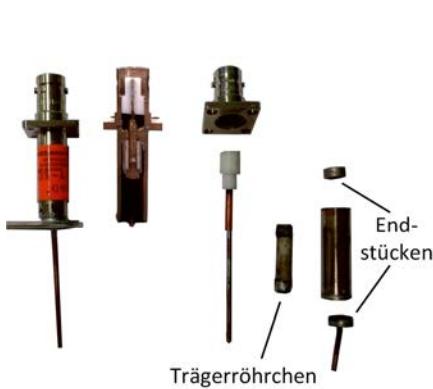

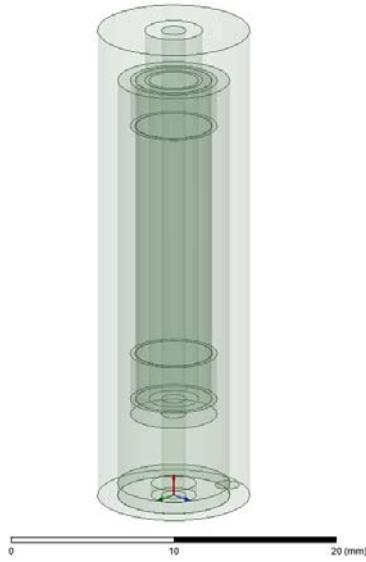

| 3.2.1 Koaxialer Messwiderstand (Koaxialshunt) .....                              | 35   |

| 3.2.2 Hair-pin-Shunt .....                                                       | 40   |

| 3.2.3 M-Shunt.....                                                               | 43   |

| 3.2.4 PCB-M-Shunt .....                                                          | 47   |

| 3.2.5 Messwiderstände im Überblick.....                                          | 48   |

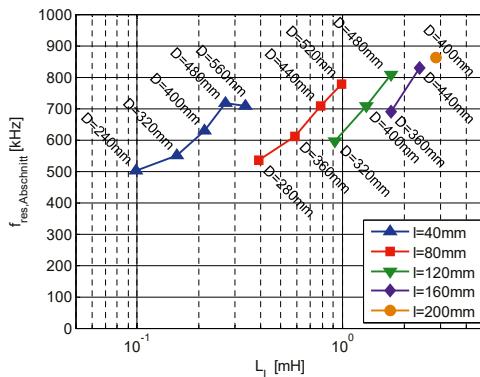

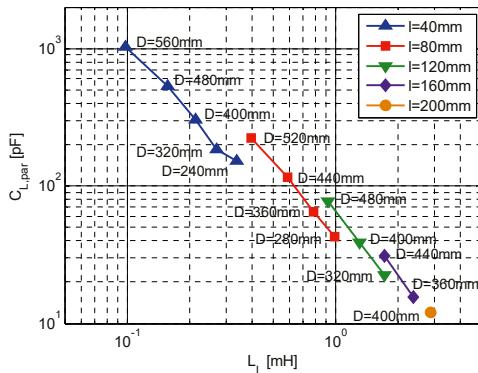

| 3.3 Lastinduktivitäten für Messaufbauten .....                                   | 49   |

| 4 Sperr- und Schaltverhalten von Dioden .....                                    | 53   |

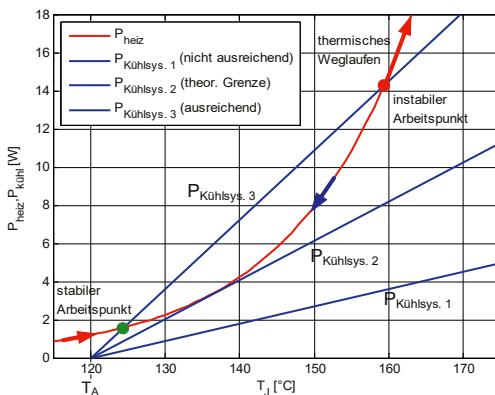

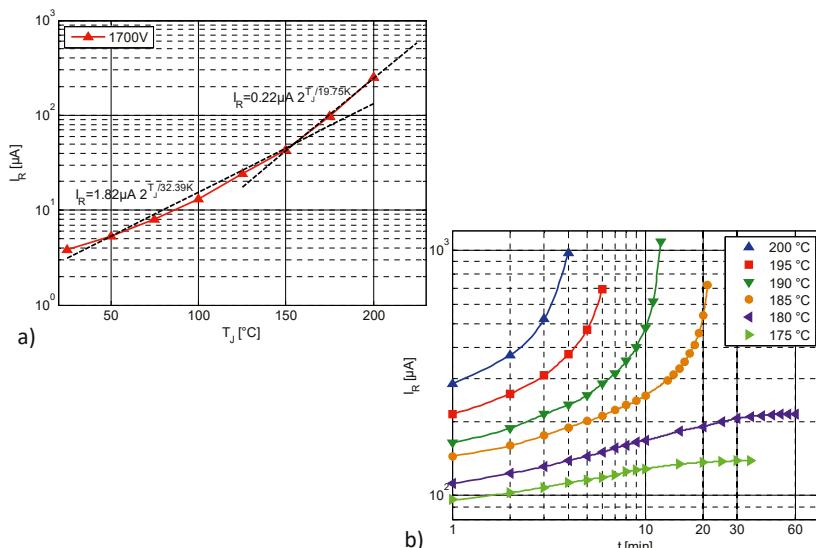

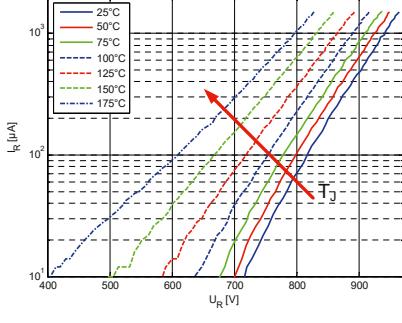

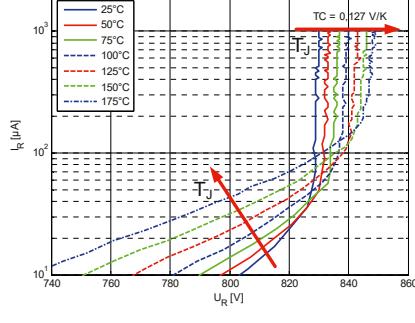

| 4.1 Thermische Stabilität von 0,6 kV bis 1,7 kV Dioden im Sperrbetrieb.....      | 53   |

| 4.1.1 Selbsterwärmung und thermisches Weglaufen .....                            | 53   |

| 4.1.2 Leckströme .....                                                           | 55   |

| 4.1.3 Ermittlung der Verdopplungstemperaturdifferenzen der Leckströme.....       | 61   |

| 4.1.4 Anwendung des Stabilitätskriteriums .....                                  | 67   |

| 4.1.5 Lawinendurchbruch in SiC im Vergleich mit Silizium und Galliumnitrid ..... | 69   |

|       |                                                                                      |     |

|-------|--------------------------------------------------------------------------------------|-----|

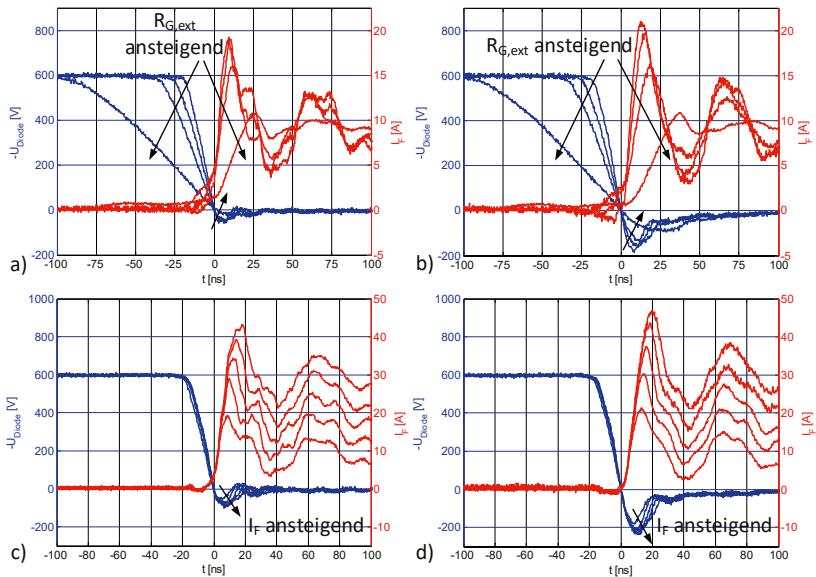

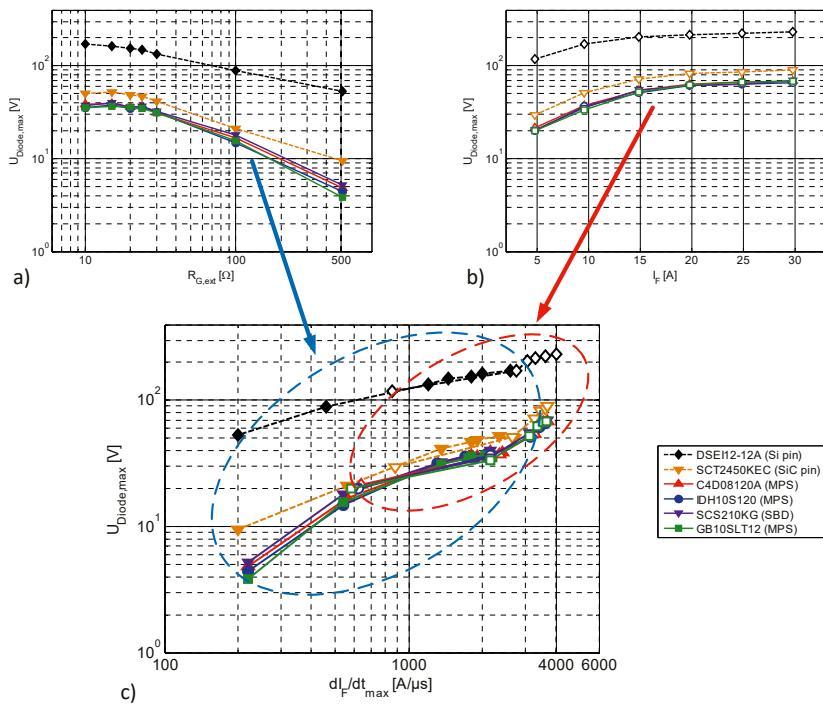

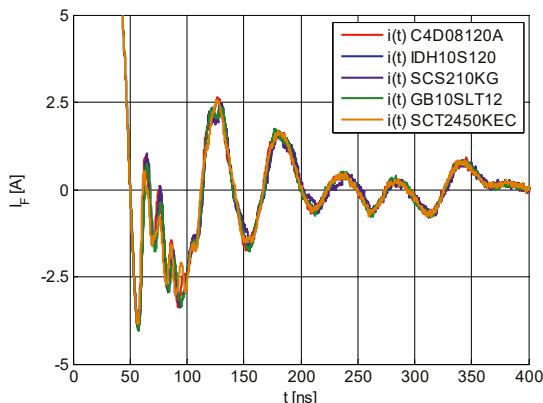

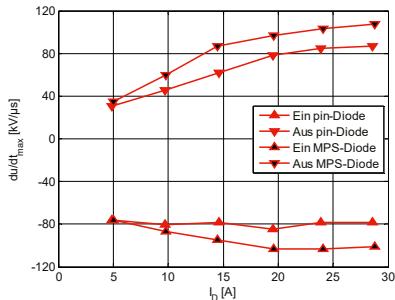

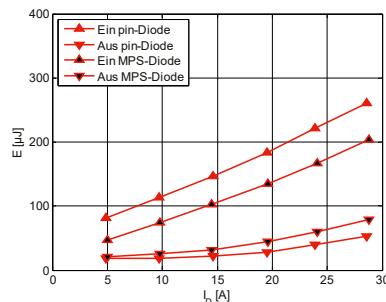

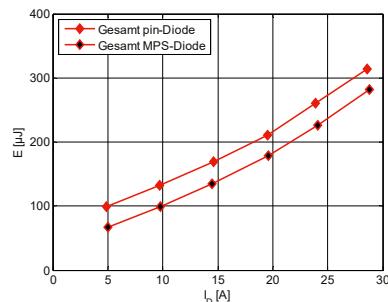

| 4.2   | Schaltverhalten von 1,2 kV Dioden .....                                              | 71  |

| 4.2.1 | Einschaltverhalten .....                                                             | 74  |

| 4.2.2 | Ausschaltverhalten .....                                                             | 77  |

| 5     | Durchlass- und Schaltverhalten von Transistoren .....                                | 82  |

| 5.1   | 1,2 kV BJT .....                                                                     | 83  |

| 5.1.1 | Durchlassverhalten .....                                                             | 83  |

| 5.1.2 | Schaltverhalten .....                                                                | 84  |

| 5.2   | 1,2 kV JFET .....                                                                    | 87  |

| 5.3   | 1,2 kV MOSFET .....                                                                  | 89  |

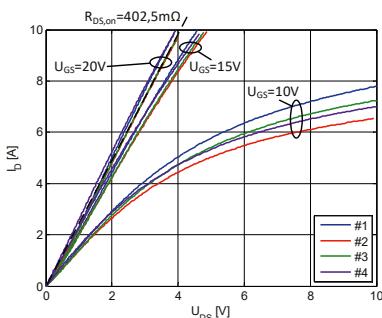

| 5.3.1 | Durchlassverhalten .....                                                             | 89  |

| 5.3.2 | Schaltverhalten .....                                                                | 94  |

| 5.4   | 3,3 kV MOSFET .....                                                                  | 114 |

| 5.4.1 | Durchlassverhalten .....                                                             | 115 |

| 5.4.2 | Schaltverhalten .....                                                                | 116 |

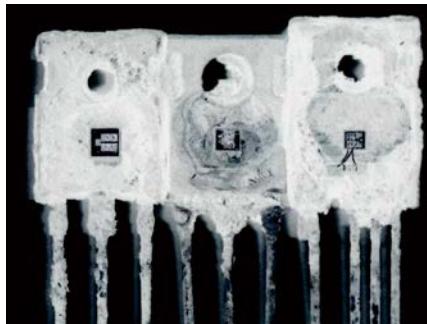

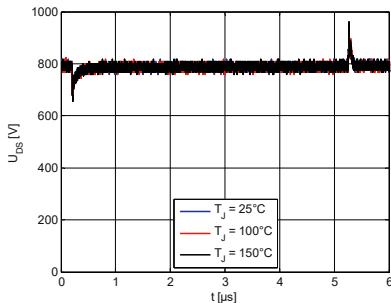

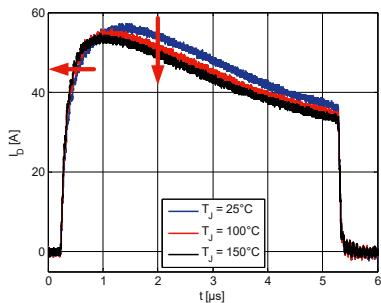

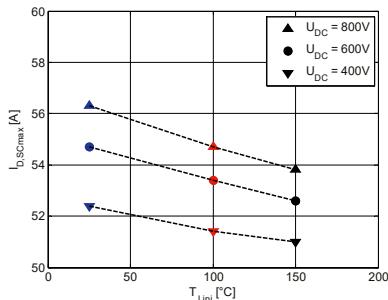

| 5.5   | Zerstörungsgrenzen beim Kurzschluss .....                                            | 117 |

| 5.6   | Überspannungsschutz .....                                                            | 126 |

| 5.6.1 | Active Clamping .....                                                                | 128 |

| 5.6.2 | Dynamic Voltage Rise Control .....                                                   | 129 |

| 5.6.3 | Dynamic Active Clamping .....                                                        | 133 |

| 6     | Zusammenfassung .....                                                                | 138 |

| 7     | Anhang .....                                                                         | 141 |

| 7.1   | Darstellung des Messplatzes .....                                                    | 141 |

| 7.2   | Wichtige Komponenten zur Durchführung der Schaltversuche .....                       | 142 |

| 7.3   | Darstellung der Messplatten für vergleichende Messungen .....                        | 143 |

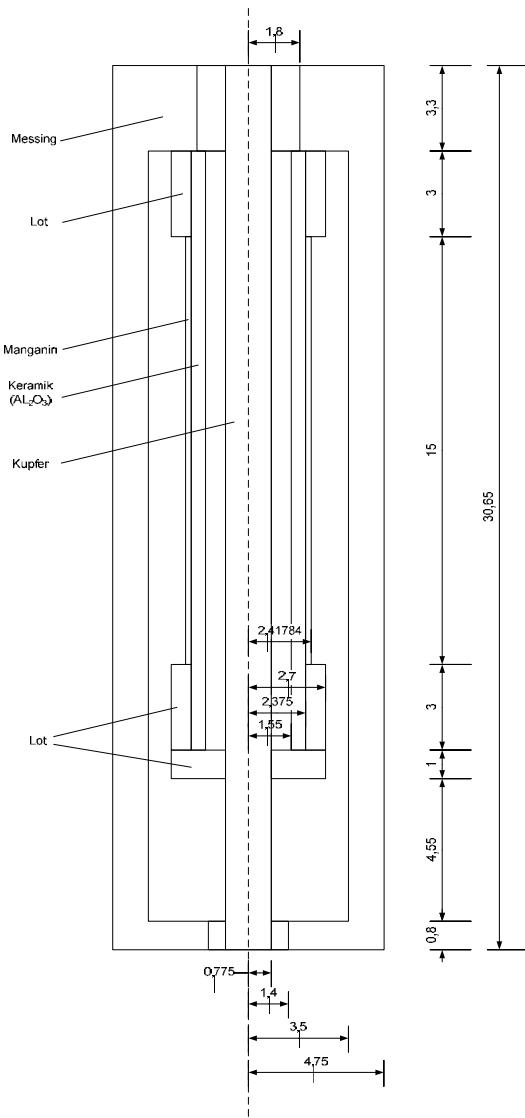

| 7.4   | Technische Zeichnung des erstellten Simulationsmodells vom Koaxialshunt .....        | 144 |

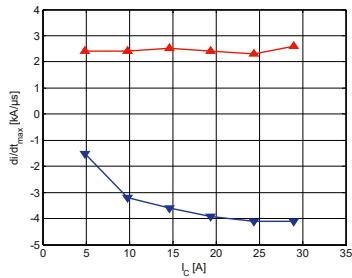

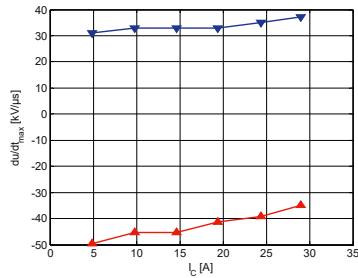

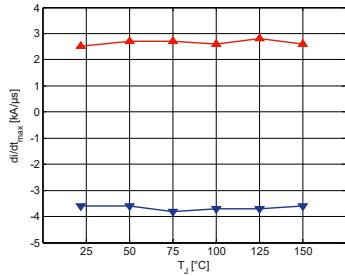

| 7.5   | SiC-BJT: Schaltgeschwindigkeiten in Abhängigkeit von $I_C$ und $T_J$ .....           | 145 |

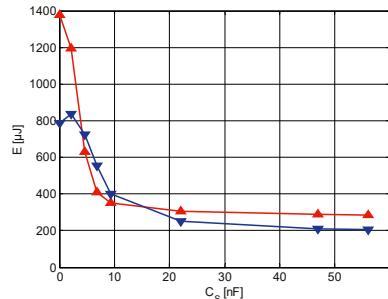

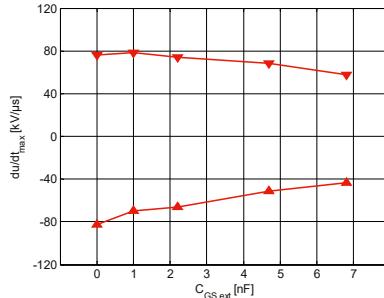

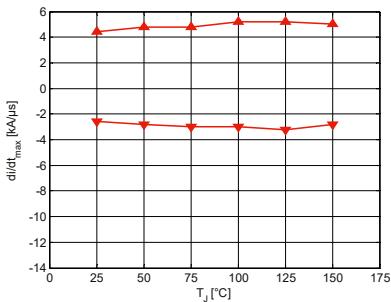

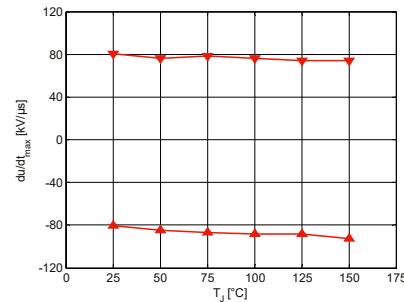

| 7.6   | SiC-MOSFET: Schaltverläufe in Abhängigkeit von $C_{GS,ext}$ .....                    | 146 |

| 7.7   | SiC-MOSFET: Schaltgeschwindigkeiten in Abhängigkeit von $C_{GS,ext}$ und $T_J$ ..... | 147 |

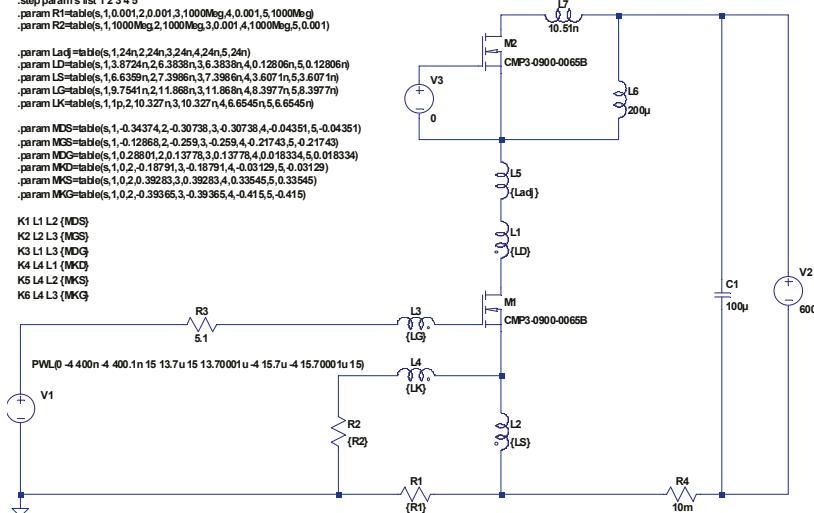

| 7.8   | SiC-MOSFET: Simulationsmodell .....                                                  | 148 |

| 8     | Literaturverzeichnis .....                                                           | 149 |

| 8.1   | Fachliteratur .....                                                                  | 149 |

| 8.2   | Datenblätter und Bedienungsanleitungen .....                                         | 160 |

| 8.3   | Betreute studentische Arbeitsvorhaben .....                                          | 164 |

# Formelzeichen und Abkürzungen

| Formelzeichen/<br>Abkürzung | Bedeutung                                      |

|-----------------------------|------------------------------------------------|

| A                           | Chipdicke                                      |

| $A^*$                       | Richardson-Konstante                           |

| $A_{\text{aktiv}}$          | Aktive Fläche des Chips                        |

| AC                          | Active Clamping                                |

| $A_{\text{Chip}}$           | Gesamtfläche eines Chips                       |

| $A_{\text{Diode}}$          | aktive Fläche der Diode                        |

| $A_{\text{Spule}}$          | Fläche einer Spule                             |

| B                           | Stromverstärkung                               |

| b                           | Breite                                         |

| BJT                         | Bipolar Junction Transistor, Bipolartransistor |

| BV                          | Breakdown Voltage, Durchbruchspannung          |

| C                           | Kapazität                                      |

| $C_{\text{DC}}$             | Zwischenkreiskapazität                         |

| $C_{\text{DS}}$             | Drain-Source-Kapazität                         |

| $C_{\text{GD}}$             | Gate-Drain-Kapazität, Miller-Kapazität         |

| $C_{\text{GS}}$             | Gate-Source-Kapazität                          |

| $C_{\text{GS,ext}}$         | externe Gate-Source-Kapazität                  |

| $C_{\text{iss}}$            | Eingangskapazität eines MOSFETs                |

| $C_j$                       | Sperrschichtkapazität                          |

| $C_{\text{komp}}$           | Kapazität des Kompensationsnetzwerks           |

| $C_{\text{koppel}}$         | Koppelkapazität                                |

| $C_{\text{L,par}}$          | parasitäre Induktivität der Lastinduktivität   |

| $C_{\text{oss}}$            | Ausgangskapazität des MOSFETs                  |

| $C_{\text{ox}}$             | Oxid-Kapazität                                 |

| $C_s$                       | Speed-Up-Kondensator                           |

| $C_{\text{th}}$             | spezifische Wärmekapazität                     |

| $C_{\text{th}}$             | Wärmekapazität, thermische Kapazität           |

| $C_\sigma$                  | parasitäre Kapazität                           |

| d                           | Dicke, Schichtdicke                            |

| $d_{\text{Chip}}$           | Chipdicke                                      |

| $d_{\text{Epitaxie}}$       | Epitaxieschichtdicke                           |

| $d_{\text{Wafer}}$          | Wafer-Dicke                                    |

| D                           | Diode                                          |

| DAC                         | Dynamic Active Clamping                        |

| $D_F$                       | Freilaufdiode                                  |

| $D_p$                       | Diffusionskoeffizient von Löchern              |

| $D_{\text{Spule}}$          | Durchmesser einer Spule                        |

| DVRC                        | Dynamic Voltage Rise Control                   |

| E                           | elektrische Feldstärke                         |

|                                          |                                                                        |

|------------------------------------------|------------------------------------------------------------------------|

| E                                        | Energie, Schaltenergie                                                 |

| $E_{\text{aus}}$                         | Ausschaltenergie                                                       |

| $E_{\text{Chip}}$                        | in einen Chip eingebrachte Energie                                     |

| $E_{\text{ein}}$                         | Einschaltenergie                                                       |

| $E_{\text{Epitaxie}}$                    | in die Epitaxieschicht eines Chips eingebrachte Energie                |

| $E_{\text{ges}}$                         | Gesamtenergie                                                          |

| $E_{\text{krit}}$                        | kritische elektrische Feldstärke                                       |

| ECPE                                     | European Center for Power Electronics e. V.                            |

| f                                        | Frequenz                                                               |

| $f_{\text{Mess}}$                        | Messfrequenz                                                           |

| $f_N$                                    | Faktor für Spuleninduktivität                                          |

| $f_{\text{res,Spule}}$                   | Resonanzfrequenz einer Spule, Resonanzfrequenz einer Lastinduktivität  |

| $f_{\text{Signal}}$                      | Signalfrequenz                                                         |

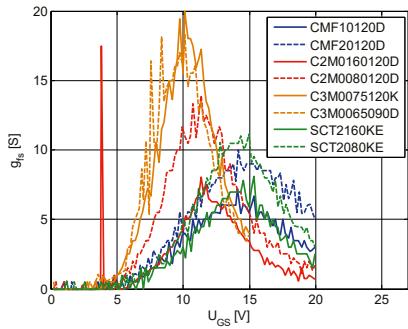

| $g_{\text{fs}}$                          | Transkonduktanz                                                        |

| H                                        | magnetische Feldstärke                                                 |

| h                                        | Plancksches Wirkungsquantum                                            |

| $h_{\text{FE}}$                          | Stromverstärkung                                                       |

| HP-Shunt                                 | Hair-pin-Shunt                                                         |

| i                                        | intrinsisches Halbleitergebiet                                         |

| $I, i$                                   | Strom                                                                  |

| IALB                                     | Institut für elektrische Antriebe, Leistungselektronik und Bauelemente |

| $I_B, i_B$                               | Basisstrom                                                             |

| $I_C, i_C$                               | Kollektorstrom                                                         |

| $I_{\text{ca}}, i_{\text{ca}}$           | Strom durch Kapazität                                                  |

| $I_D, i_D$                               | Drain-Strom                                                            |

| $i_{D,\text{Leck}}$                      | Drain-Source-Leckstrom                                                 |

| $i_{\text{DSC}}, i_{\text{DSC}}$         | Drain-Strom im Kurzschlussfall                                         |

| $i_{\text{DSC,max}}, i_{\text{DSC,max}}$ | maximaler Drain-Strom im Kurzschlussfall                               |

| $i_E, i_E$                               | Emitterstrom                                                           |

| $I_F, i_F$                               | Strom durch Freilaufdiode                                              |

| $I_G, i_G$                               | Gate-Strom                                                             |

| $i_{G,\text{Leck}}$                      | Gate-Leckstrom                                                         |

| IGBT                                     | Insulated Gate Bipolar Transistor                                      |

| $i_{\text{komp}}$                        | Strom durch ein Kompensationsnetzwerk                                  |

| $I_L, i_L$                               | Strom durch Lastinduktivität                                           |

| $I_{\text{Nenn}}$                        | Nennstrom                                                              |

| $I_R$                                    | Leckstrom                                                              |

| $i_{\text{Referenz}}$                    | Strom eines Referenzshunts                                             |

| $i_{\text{RR}}$                          | Rückstrom                                                              |

| $i_{\text{RRM}}$                         | Rückstromspitze                                                        |

| $I_S, i_S$                               | Source-Strom                                                           |

| $I_{\text{SC}}, i_{\text{SC}}$           | Kurzschlussstrom                                                       |

| $i_{\text{Shunt}}$                       | Shuntstrom                                                             |

|                                 |                                                                                    |

|---------------------------------|------------------------------------------------------------------------------------|

| $I_{\text{Test}}$               | Teststrom                                                                          |

| $J, j$                          | Stromdichte                                                                        |

| $\text{JFET}$                   | Junction Field Effekt Transistor, Sperrschiichtfeldeffekttransistor                |

| $J_F, j_F$                      | Stromdichte im Durchlassbetrieb einer Diode                                        |

| $J_{\text{Generation}}$         | Generationsleckstromdichte                                                         |

| $J_R, j_R$                      | Leckstromdichte                                                                    |

| $J_S$                           | Diffusionsleckstromdichte                                                          |

| $J_{\text{TFE}}$                | Leckstrom durch thermionische Feldemission                                         |

| $k_B$                           | Boltzmann-Konstante                                                                |

| $K_{XY}$                        | Koppelfaktor der Induktivitäten $L_x$ und $L_y$ mit der Gegeninduktivität $M_{XY}$ |

| $l$                             | Länge                                                                              |

| $L_{\text{Kanal}}$              | Kanallänge                                                                         |

| $l_{\text{Spule}}$              | Länge der Spule                                                                    |

| $L$                             | Induktivität                                                                       |

| $L^a$                           | äußere Induktivität zwischen zwei Leitern (koaxiale Anordnung)                     |

| $L_B$                           | Basis-Induktivität                                                                 |

| $L_C$                           | Kollektor-Induktivität                                                             |

| $L_D$                           | Drain-Induktivität                                                                 |

| $L_E$                           | Emitter-Induktivität                                                               |

| $L_G$                           | Gate-Induktivität                                                                  |

| $L_i^i$                         | innere Induktivität eines äußeren Leiters (koaxiale Anordnung)                     |

| $L_i^i$                         | innere Induktivität eines Leiters (koaxiale Anordnung)                             |

| $L_{i,\text{hohl}}^i$           | innere Induktivität eines inneren hohlen Leiters (koaxiale Anordnung)              |

| $L_{i,\text{massiv}}^i$         | innere Induktivität eines inneren massiven Leiters (koaxiale Anordnung)            |

| $L_{KS}$                        | Kelvin-Source-Induktivität                                                         |

| $L_L$                           | Lastinduktivität, Lastspule                                                        |

| $L_{\text{Mess}}$               | Induktivität des Messkreises                                                       |

| $L_s$                           | Source-Induktivität                                                                |

| $L_{\text{Shunt}}$              | Induktivität eines Shunts, Streuinduktivität eines Shunts                          |

| $L_{\text{Shunt},\text{ber}}$   | berechnete Induktivität eines Shunts                                               |

| $L_{\text{Shunt},\text{ideal}}$ | ideale Induktivität eines Shunts                                                   |

| $L_{\text{Shunt},\text{sim}}$   | simulierte Induktivität eines Shunts                                               |

| $L_o$                           | parasitäre Induktivität, Streuinduktivität                                         |

| $L_{o,\text{Diode}}$            | Induktivität zwischen Dioden-Chip und Gehäuseanschlüssen                           |

| $M$                             | Metall-Oxid-Halbleiter-Feldeffekttransistor                                        |

| $m$                             | Masse                                                                              |

| $m$                             | effektive Elektronenmasse                                                          |

| $m_0$                           | Elektronenmasse                                                                    |

| $m_{\text{Chip}}$               | Chipmasse                                                                          |

| $M_{\text{MESS}}$               | Gegeninduktivität des Messkreises                                                  |

| $\text{MOSFET}$                 | Metall-Oxid-Halbleiter-Feldeffekttransistor                                        |

| $n$                             | Anzahl der Messpunkte zur Filterung mittels gleitender Mittelwertbildung           |

| $n, n^-, n^+$                   | n-dotiertes Halbleitergebiet                                                       |

|                 |                                                                            |

|-----------------|----------------------------------------------------------------------------|

| $N_D$           | Dichte der Donatoren                                                       |

| $n_i$           | intrinsische Ladungsträgerdichte                                           |

| $n_w$           | Windungszahl                                                               |

| $p, p^-, p^+$   | p-dotiertes Halbleitergebiet                                               |

| PCB             | Printed Circuit Board, Leiterplatte                                        |

| $P_R$           | Verlustleistung im Sperrbetrieb                                            |

| $P_{SC}$        | Verlustleistung während eines Kurzschlusses                                |

| $P_{Shunt}$     | umgesetzte Verlustleistung in einem Shunt                                  |

| $P_V$           | Verlustleistung                                                            |

| $q$             | Elementarladung                                                            |

| $Q$             | Bipolartransistor                                                          |

| $Q_C$           | Sperrsichtladung                                                           |

| $Q_{RR}$        | Sperrverzögerungsladung                                                    |

| $Q_{th}$        | Wärmemenge                                                                 |

| $r$             | Radius                                                                     |

| $R$             | Widerstand                                                                 |

| $R_{Abschluss}$ | Abschlusswiderstand                                                        |

| $R_B$           | Basis-Widerstand                                                           |

| $r_{CE,on}$     | Durchlasswiderstand eines BJTs                                             |

| $r_{on}$        | spezifischer Widerstand                                                    |

| $r_{CE,on}$     | spezifischer Durchlasswiderstand eines BJTs                                |

| $r_{DS,on}$     | spezifischer Durchlasswiderstand eines MOSFETs beziehungsweise eines JFETs |

| $R_{DS,on}$     | Durchlasswiderstand eines MOSFETs beziehungsweise eines JFETs              |

| $R_G$           | Gate-Widerstand                                                            |

| $R_{G,ext}$     | externer Gate-Widerstand                                                   |

| $R_{G,int}$     | interner Gate-Widerstand                                                   |

| $R_{G,ges}$     | Gesamt-Gate-Widerstand                                                     |

| $R_{Koax}$      | Widerstand eines Koaxialshunts                                             |

| $R_{komp}$      | Widerstand eines Kompensationsnetzwerks                                    |

| $R_{Kontakt}$   | Kontaktwiderstand, Übergangswiderstand                                     |

| $R_{min}$       | Mindestwiderstand im Ansteuerkreis                                         |

| $R_S$           | Widerstand im Speed-Up-Zweig einer Ansteuerschaltung                       |

| $R_{Shunt}$     | Widerstand eines Shunts                                                    |

| $R_{Shunt,Ref}$ | Widerstand eines Referenzshunts                                            |

| $R_{th,JA}$     | thermischer Widerstand zwischen Sperrsicht und Umgebung                    |

| SC              | Short Circuit, Kurzschluss                                                 |

| Si              | Silizium                                                                   |

| SiC             | Siliziumkarbid                                                             |

| $S_{Shunt}$     | Standardabweichung von $L_{Shunt}$                                         |

| T               | Transistor                                                                 |

| T               | Temperatur                                                                 |

| $T_A$           | Umgebungstemperatur                                                        |

| $T_{A,0}$       | Umgebungstemperatur                                                        |

|                            |                                                            |

|----------------------------|------------------------------------------------------------|

| $T_{A,krit}$               | kritische Umgebungstemperatur                              |

| $T_J$                      | Sperrsichttemperatur                                       |

| $T_{J,ini}$                | initiale Sperrsichttemperatur                              |

| $\text{TC}$                | Temperaturkoeffizient                                      |

| $t$                        | Zeit                                                       |

| $t_{SC}$                   | Kurzschlusszeit beziehungsweise -dauer                     |

| $t_{SC,krit}$              | kritische Kurzschlusszeit beziehungsweise -dauer           |

| $t_{\Delta E}$             | Zeitdauer, in der Energie entnommen wird                   |

| $U_{BE}, U_{BE}$           | Basis-Emitter-Spannung                                     |

| $U_{CB}, U_{CB}$           | Kollektor-Basis-Spannung                                   |

| $U_{CE}, U_{CE}$           | Kollektor-Emitter-Spannung                                 |

| $U_{DC}$                   | Zwischenkreisspannung                                      |

| $U_{DS}, U_{DS}$           | Drain-Source-Spannung                                      |

| $U_{DS,ein}$               | Drain-Source-Spannung im Durchlassfall                     |

| $U_{FRM}$                  | Durchlassverzögerungsspannung                              |

| $U_{GKS}$                  | Gate-Kelvin-Source-Spannung                                |

| $U_{GS}, U_{GS}$           | Gate-Source-Spannung                                       |

| $U_{GS,Miller}$            | Spannung des Miller-Plateaus                               |

| $U_{komp}, U_{komp}$       | kompensiertes Spannungssignal                              |

| $U_{Kontakt}$              | Kontaktspannung                                            |

| $U_{korrigiert}$           | korrigiertes Spannungssignal                               |

| $U_L$                      | induktiver Spannungsanteil im Messsignal                   |

| $U_{Lo}, U_{Lo}$           | Überspannung an Induktivität                               |

| $U_Q$                      | Quellenspannung                                            |

| $U_{Q,erhöht}$             | erhöhte Quellenspannung                                    |

| $U_R$                      | ohmscher Spannungsanteil im Messsignal                     |

| $U_R$                      | Sperrspannung                                              |

| $U_{R,max}$                | maximale Sperrspannung beziehungsweise Sperrfähigkeit      |

| $U_S$                      | Spannung an der Induktivität $L_S$                         |

| $U_{Shunt}$                | Spannung am Shunt, Messspannung am Shunt                   |

| $U_{Signal}$               | Signalspannung                                             |

| $U_{th}$                   | Schwellenspannung                                          |

| $U_{Treiber}, U_{Treiber}$ | Treiberspannung                                            |

| $U_{o,Diode}$              | von $L_{o,Diode}$ bedingte Spannung                        |

| $V_{Chip}$                 | Chipvolumen                                                |

| $V_{sat}$                  | Sättigungsgeschwindigkeit                                  |

| $W$                        | Weite                                                      |

| $w$                        | Driftgebiete weite                                         |

| $W_g$                      | Bandlücke                                                  |

| $W_{RLZ}$                  | Weite der Raumladungszone, Weite der Sperrsicht            |

| $Z$                        | Wellenwiderstand                                           |

| $\alpha$                   | Temperaturkoeffizient                                      |

| $\alpha_{20}$              | Temperaturkoeffizient eines Widerstandsmaterials bei 20 °C |

|                      |                                                   |

|----------------------|---------------------------------------------------|

| $\alpha_T$           | Transportfaktor                                   |

| $\gamma$             | Emitter-Effizienz                                 |

| $\delta$             | Eindringtiefe                                     |

| $\Delta E$           | Energiedifferenz, Energieentnahme                 |

| $\Delta E_{SC,krit}$ | Differenz zweier kritischer Kurzschlussenergien   |

| $\Delta R_{Shunt}$   | Widerstandsänderung                               |

| $\Delta T$           | Temperaturänderung                                |

| $\Delta T_d$         | Verdopplungs temperaturdifferenz                  |

| $\Delta T_J$         | Sperrsichttemperaturänderung                      |

| $\Delta U$           | Spannungsversatz                                  |

| $\Delta U_{DC}$      | Abfall der Zwischenkreisspannung                  |

| $\epsilon$           | Dielektrizitätskonstante                          |

| $\epsilon_R$         | relative Permittivität                            |

| $\Theta$             | Durchflutung                                      |

| $\lambda$            | Wärmeleitfähigkeit                                |

| $\mu$                | Permeabilität                                     |

| $\mu_0$              | Permeabilitätskonstante                           |

| $\mu_r$              | relative Permeabilität                            |

| $\mu_n$              | Elektronenbeweglichkeit                           |

| $\mu_n^*$            | Elektronenbeweglichkeit im Kanal                  |

| $\mu_p$              | Löcherbeweglichkeit                               |

| $\rho$               | spezifischer elektrischer Widerstand              |

| $\rho$               | Dichte eines Materials                            |

| $\rho_{20}$          | spezifischer Widerstand eines Materials bei 20 °C |

| $\sigma$             | Leitfähigkeit                                     |

| $\tau_g$             | Generationsträgerlebensdauer                      |

| $\tau_p$             | Lebensdauer der Löcher                            |

| $\varphi_B$          | Barrierenhöhe                                     |

| $\omega$             | Kreisfrequenz                                     |

---

## Kurzfassung

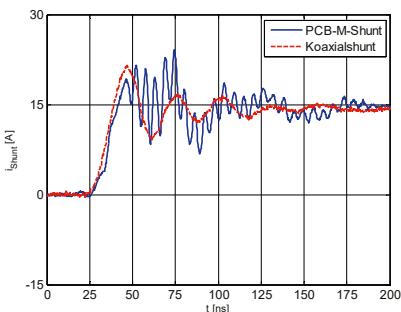

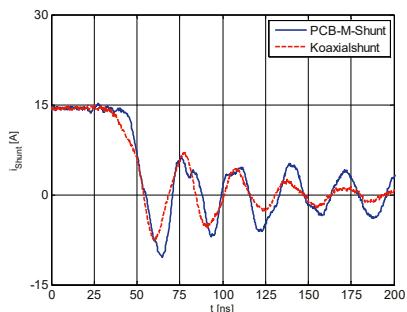

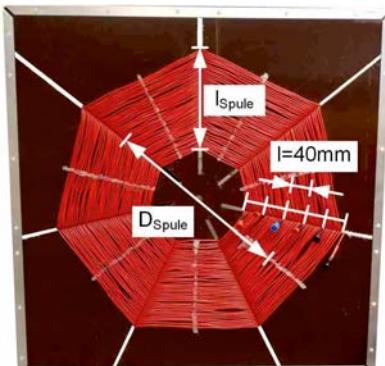

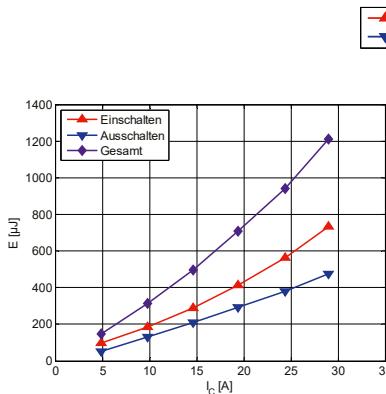

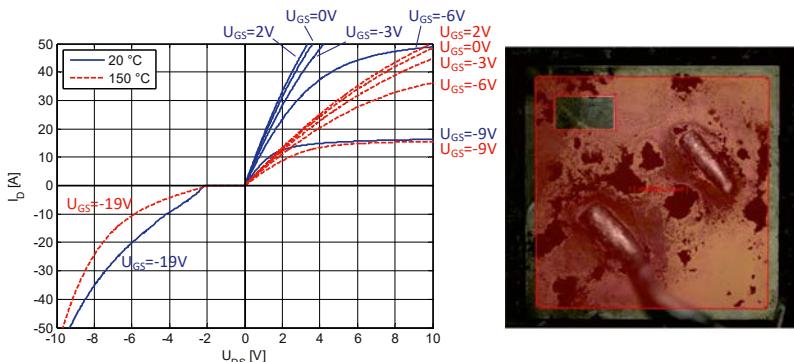

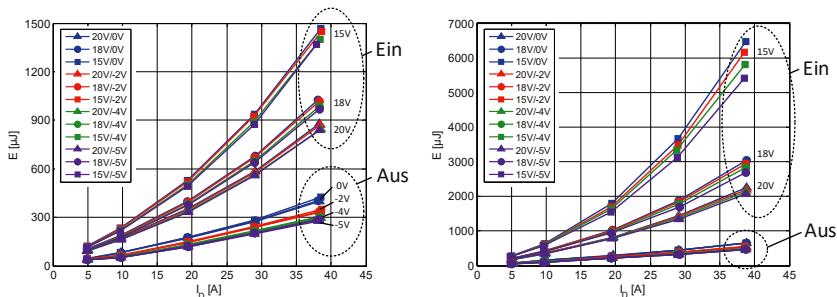

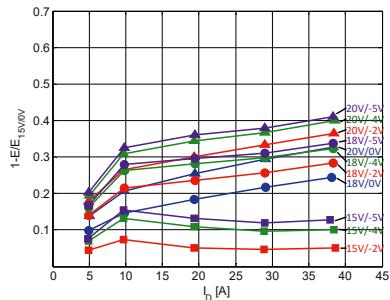

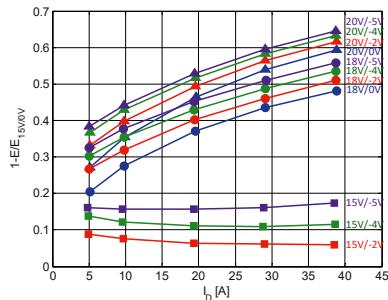

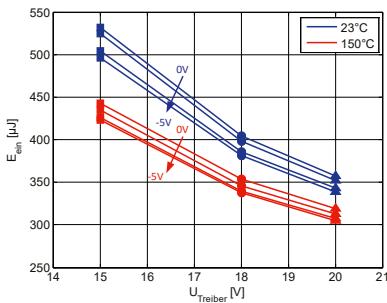

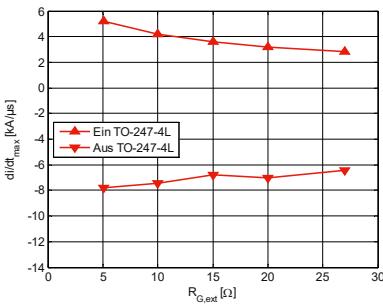

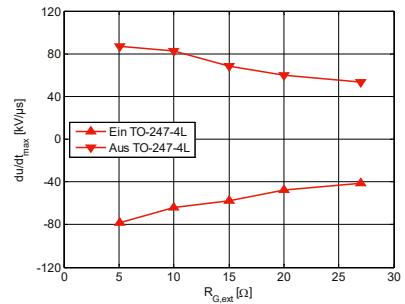

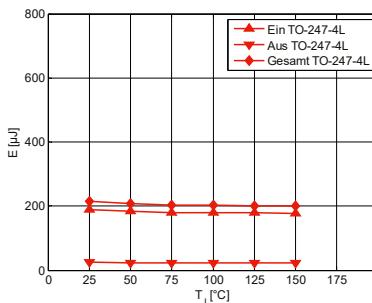

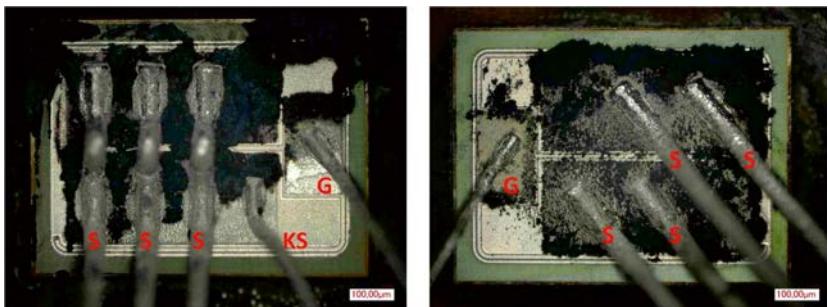

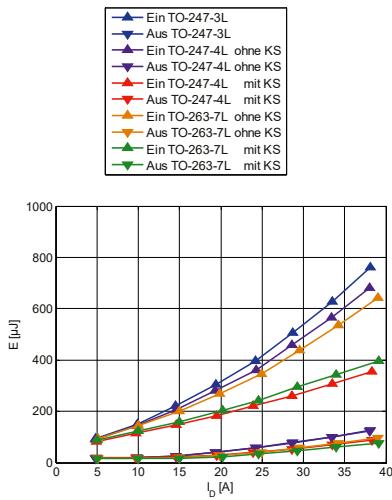

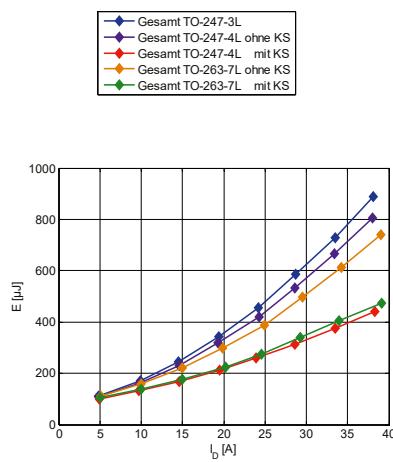

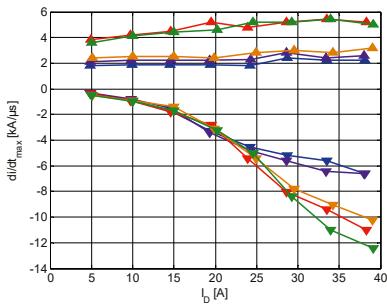

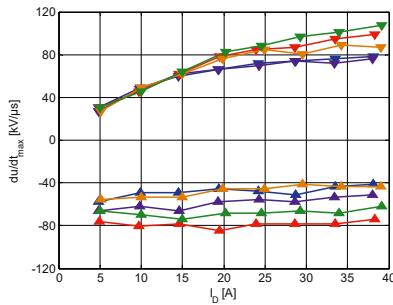

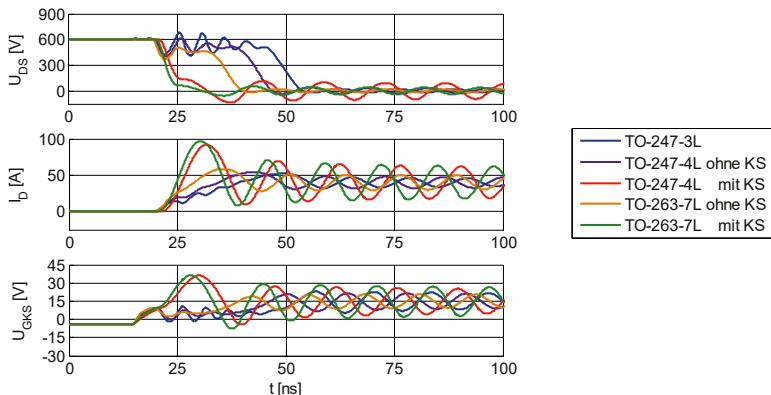

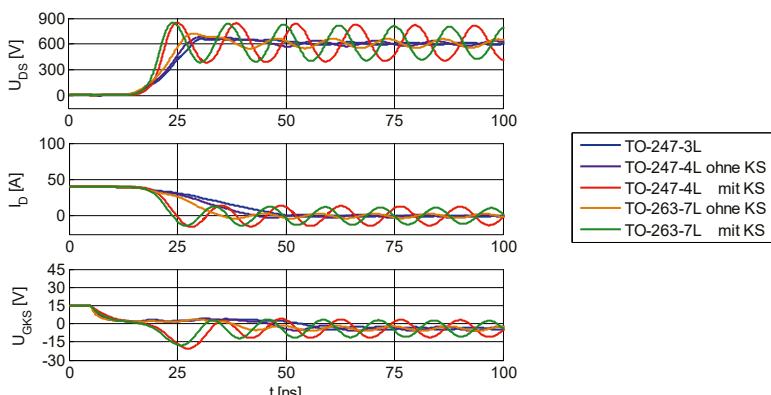

Die vorliegende Arbeit beschäftigt sich mit den extrinsischen - somit von der Gehäuse- sowie Schaltungsumgebung bedingten - und den intrinsischen - also vom Chip herrührenden - Beeinflussungen des Verhaltens von Leistungshalbleiterbauelementen aus Siliziumkarbid (SiC). Zunächst werden deren strukturelle Eigenschaften und die Auswirkungen parasitärer Elemente allgemein betrachtet. Anschließend erfolgt eine Zusammenfassung der für die Charakterisierung verwendeten Messschaltungen sowie der durch notwendige Bestandteile der Schaltung eingebrachten parasitären Elemente. Es wird dabei unter anderem der planare M-Shunt, der mit dem Koaxialshunt verwandt ist, untersucht. Den Messergebnissen zufolge weist der M-Shunt - wie angestrebt - eine deutlich geringere Streuinduktivität auf als der häufig in Messschaltungen genutzte Koaxialshunt. Die Charakterisierung der SiC-Dioden und SiC-Transistoren wird mittels statischer und dynamischer Messmethoden, das heißt mit unterschiedlichen Kennlinienschreibern und einem Doppelpulsmessplatz, durchgeführt. Der Sperrbetrieb der Dioden wird im Hinblick auf die thermische Stabilität untersucht und die Leckströme werden in Abhängigkeit der Sperrsichttemperatur beschrieben. Ein wesentliches Ergebnis der Messungen ist, dass die thermische Stabilität der SiC-Dioden nur unter atypischen Umgebungsbedingungen hinterfragt werden muss beziehungsweise gefährdet ist. Demgegenüber werden bei der dynamischen Charakterisierung der Dioden die Einschaltüberspannung sowie die zu extrahierende Ladung beim Ausschalten bestimmt. Abschließend werden die ermittelten Kenngrößen jeweils mit den entsprechenden Werten von Silizium-Dioden verglichen. Bei den statischen Messungen der SiC-Transistoren wird das Durchlassverhalten hinsichtlich verschiedener Transistorarten sowie herstellerbedingter Unterschiede beim SiC-MOSFET aufgezeigt. Die dynamische Vermessung der Transistoren umfasst eine Analyse des Einflusses der Ansteuerparameter, der Gehäuse, der Sperrsichttemperatur und unterschiedlicher SiC-Freilaufdioden auf das Schaltverhalten beziehungsweise auf die Schaltenergien. Mit Hilfe der Messungen lässt sich unter anderem quantitativ zeigen, wie groß der Vorteil von mit Kelvin-Source-Anschluss ausgestatteten Gehäusen gegenüber klassischen Gehäusen wie dem TO-247-3L-Gehäuse ist. Allerdings wird anhand ergänzend durchgeföhrter Simulationen auch ersichtlich, dass es bei den mit einem Kelvin-Source-Anschluss aufgewerteten Gehäusen zu neuen Beeinflussungen beziehungsweise auch Einschränkungen kommt, da diese zum Teil in der verwendeten Schaltung eine Zunahme der Streuinduktivitäten hervorrufen. Des Weiteren werden die Zerstörungsgrenzen von SiC-MOSFETs untersucht und das Kurzschlussverhalten beschrieben. Abschließend wird die Anwendbarkeit unterschiedlicher Überspannungsschutzbeschaltungen auf SiC-MOSFETs analysiert. Hierbei zeigt sich, dass insbesondere die von Silizium-IGBTs bekannte Dynamic Active Clamping-Beschaltung auch bei SiC-MOSFETs zu guten Ergebnissen führt.

## Abstract

The present work deals with the extrinsic - thus dependent on the package and the surrounding circuit - and the intrinsic - thus caused by the chip - effects on the behaviour of silicon carbide (SiC) power semiconductor devices. First, their structural properties and the effects of parasitic elements are generally considered. This is followed by a summary of the measuring circuits used for the characterisation as well as the parasitic elements introduced by necessary components of the circuit. Among other things, the planar M-shunt is investigated, which is related to the coaxial shunt. According to the measurement results, the M-shunt has - as desired - a significantly lower stray inductance than the coaxial shunt that is frequently used in measurement circuits. The characterisation of the SiC diodes and SiC transistors is carried out by means of static and dynamic measuring methods, i. e. with different curve tracers and a double pulse test bench. The blocking operation of diodes is examined regarding the thermal stability and the leakage currents are described as a function of the junction temperature. An essential result of the measurements is that the thermal stability of SiC diodes only has to be questioned under atypical environmental conditions and is endangered under these, respectively. In contrast, by dynamic characterisation of the diodes, the turn-on overvoltage and the charge to be extracted during turn-off are determined. Finally, the investigated values are compared with the corresponding values of silicon diodes. Static measurements of SiC transistors show the on-state behaviour regarding different transistor types as well as manufacturer specific differences for SiC-MOSFETs. The dynamic characterisation of the transistors comprises an analysis of the impact of the drive parameters, the housing, the junction temperature and different SiC freewheeling diodes on the switching behaviour and the switching energies, respectively. The measurements show i. a. quantitatively the great advantage of housings with Kelvin source connection over the classical TO-247-3L housing. However, based on additional simulations, it becomes apparent that new influences and restrictions arise due to the usage of the housings with Kelvin source connection, since in some cases these lead to higher stray inductances in the used circuit. Furthermore, the destruction limits of SiC-MOSFETs are investigated and the short-circuit behaviour is described. Finally, the application of different overvoltage protection circuits to SiC-MOSFETs is analysed. It is shown that in particular the dynamic active clamping circuit, which is known from silicon IGBTs, leads also to good results for SiC-MOSFETs.

# 1 Einleitung

Leistungshalbleiterbauelemente aus Siliziumkarbid (SiC) zeichnen sich durch eine verbesserte Leistungsfähigkeit gegenüber Silizium-Bauelementen aus. Die Begründung liegt in der großen Bandlücke des Materials SiC. Seit dem Aufkommen erster kommerzieller SiC-Leistungshalbleiterbauelemente hat es eine stetige Weiterentwicklung gegeben. Nachdem anfangs unterschiedliche Bauteilkonzepte für Transistoren von neuen als auch etablierten Halbleiterherstellern verfolgt wurden, hat sich der Markt in den letzten Jahren bereinigt. Der SiC-Metall-Oxid-Halbleiterfeldeffekttransistor (SiC-MOSFET) ist das beherrschende Bauelement im Bereich der Transistoren in der Spannungsklasse von 1,2 kV und hat sich nach Widerlegung der Bedenken in Hinblick auf den langfristigen Einsatz gegenüber dem SiC-Bipolartransistor (SiC-BJT) und dem SiC-Sperrschiichtfeldeffekttransistor (SiC-JFET) durchgesetzt. Im Segment der kommerziellen SiC-Dioden ist die SiC-Schottky-Diode aufgrund der Unipolarität und der niedrigen Durchlassspannung das dominierende Bauteil, wobei unterschiedliche Auslegungen der SiC-Schottky-Diode existieren. Mit der vorliegenden Arbeit soll ein Überblick über die extrinsischen - von der Schaltumgebung verursachten - sowie die intrinsischen - von dem selbst Halbleiterbauelement verursachten - Einflüsse auf das Verhalten von SiC-Leistungshalbleitern gegeben werden.

Die Transistoren und Dioden stehen in Wechselwirkung mit ihrer Schaltungsumgebung. Das heißt parasitäre und bewusst eingebrachte Elemente beeinflussen das Verhalten der SiC-Bauelemente, wobei die Leistungshalbleiter durch die intrinsischen Eigenschaften im Betrieb auch Auswirkungen auf weitere aktive und passive Komponenten haben. Deshalb werden in Abschnitt 2 zunächst die strukturellen Eigenschaften der in dieser Arbeit untersuchten Leistungshalbleiter sowie die wichtigsten parasitären Elemente und deren Auswirkung auf das Schaltverhalten betrachtet.

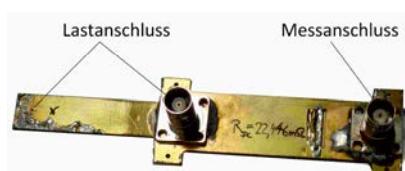

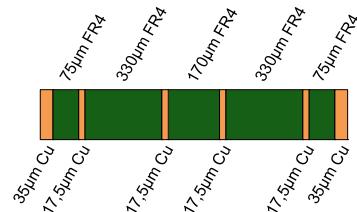

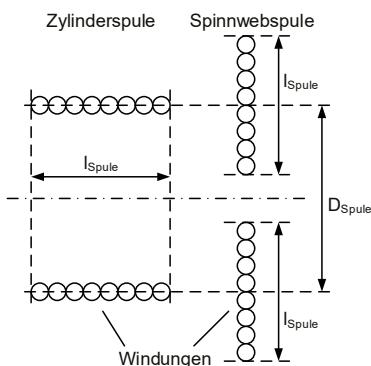

Die Voraussetzungen für die messtechnische Untersuchung der Transistoren und Dioden werden in Abschnitt 3 dargelegt. Im Speziellen wird auf die Minimierung der parasitären Induktivitäten von Messwiderständen und parasitären Kapazitäten von Lastinduktivitäten eingegangen. Es erfolgt eine Analyse verschiedener Messwiderstandsstrukturen, wobei der in der Messtechnik weitverbreitete Koaxialshunt als Referenz verwendet wird. Im Hinblick auf die bei dynamischen Schaltversuchen eingesetzten Spinnwebspulen wird deren parasitäre Kapazität an einer segmentierten Spule gemessen und strukturbezogen bewertet.

In Abschnitt 4 wird zunächst der Sperrbetrieb von SiC-Dioden im Hinblick auf die thermische Stabilität und die somit gegebene Relevanz dieses Betriebspunkts für leistungselektronische Systeme betrachtet. Des Weiteren werden die durch die SiC-Dioden selbst verursachten parasitären Effekte während des Schaltbetriebs untersucht. Alle Ergebnisse zum Sperr- und Schaltverhalten der SiC-Dioden werden mit denen von Silizium-pin-Dioden verglichen.

Eine Analyse des Verhaltens von SiC-Transistoren wird in Abschnitt 5 vorgenommen. Damit ein Vergleich zu anderen Bauteilkonzepten durchgeführt werden kann, wird neben dem SiC-MOSFET kurz auf den SiC-BJT und den SiC-JFET eingegangen. Der SiC-MOSFET wird im

Detail hinsichtlich des Einflusses der Ansteuerung, der Sperrschichttemperatur, des Gehäuses und der verwendeten Freilaufdiode vermessen. Im Weiteren werden die Belastungsfähigkeit eines SiC-MOSFETs anhand von Kurzschlussversuchen betrachtet und die Einsatzmöglichkeiten von bekannten Überspannungsschutzbeschaltungen aus dem Bereich der Silizium-IGBT-Module erörtert. Einen Ausblick auf höhersperrende Leistungshalbleiterbauelemente geben abschließend die Durchlass- und Schaltversuche an einem 3,3 kV SiC-MOSFET.

## 2 Grundlagen der Siliziumkarbid-Bauelemente

Das Grundlagenkapitel soll für die im Rahmen dieser Arbeit durchgeführten Untersuchungen beziehungsweise Betrachtungen in Abschnitt 2.1 die wichtigsten Eigenschaften von SiC als Halbleitermaterial - wie zum Beispiel auch ähnlich in [Bali08] [Lutz12] [KiCo14] beschrieben - sowie in Abschnitt 2.2 die SiC-typischen Eigenschaften der jeweiligen Leistungshalbleiterbauelemente zusammenfassen. Die exakte Funktionsweise der in Abschnitt 2.2 vorgestellten Halbleiterbauelemente wurde hinreichend in Lehr- und Applikationshandbüchern wie beispielsweise [Sze02] [Reis05] [Bali08] [Lutz12] [KiCo14] [VoHo12] diskutiert. Aus diesem Grund soll an dieser Stelle auf eine weitreichende Erklärung der generellen Funktionsweise verzichtet werden. Es erfolgt lediglich eine zusammenfassende Betrachtung beziehungsweise Darstellung der konkreten Strukturen der Halbleiterbauelemente und deren spezifischer Eigenschaften. Auch wird ein Einblick in die Ansteuerung von Transistoren gegeben. Im Weiteren wird aufgeführt, wie parasitäre Elemente sich im Speziellen auf das Schaltverhalten auswirken.

### 2.1 Materialeigenschaften

Die grundlegenden Parameter des Halbleitermaterials SiC sind im Vergleich zu Silizium in Tabelle 2.1 aufgeführt. Diese Parameter definieren das Durchlass-, Sperr- und Schaltverhalten sowie das damit in Verbindung stehende Temperaturverhalten der in SiC realisierten Halbleiterbauelemente.

Entscheidend für die Höhe der kritischen Feldstärke  $E_{\text{krit}}$  und der intrinsischen Ladungsträgerdichte  $n_i$  des jeweiligen Halbleitermaterials ist die Bandlücke  $W_g$ , welche für SiC größer ist, als jene von Silizium. Die im Vergleich zu Silizium entsprechend höhere Feldstärke  $E_{\text{krit}}$  des SiC gestattet es, dass eine Erhöhung der Dotierung  $N_D$  des Driftgebiets und eine Verminderung

**Tabelle 2.1: Parameter von Siliziumkarbid (SiC) in der 4H-Kristallstruktur im Vergleich zu Silizium (Si) bei 300 K; gemäß [SzNg07] [KiCo14]**

| Parameter         |                        | Silizium          | 4H-SiC                        | 4H-SiC                        |

|-------------------|------------------------|-------------------|-------------------------------|-------------------------------|

|                   |                        |                   | senkrecht zur c-Achse         | parallel zur c-Achse          |

| $W_g$             | eV                     | 1,12              | 3,26                          | 3,26                          |

| $E_{\text{krit}}$ | MV/cm                  | 0,25-0,8          | 2,2                           | 2,8                           |

| $\epsilon_r$      |                        | 11,9              | 9,76                          | 10,32                         |

| $v_{\text{sat}}$  | cm/s                   | $1 \cdot 10^7$    | $2,2 \cdot 10^7$ (Elektronen) | $2,2 \cdot 10^7$ (Elektronen) |

| $\mu_n$           | cm <sup>2</sup> /(V·s) | 1450              | 1020                          | 1200                          |

| $\mu_p$           | cm <sup>2</sup> /(V·s) | 500               | 120                           | 120                           |

| $n_i$             | cm <sup>-3</sup>       | $9,65 \cdot 10^9$ | $5 \cdot 10^9$                | $5 \cdot 10^9$                |

| $\lambda$         | W/(cm·K)               | 1,56              | 3,3 ... 4,9                   | 3,3 ... 4,9                   |

Werte der Parameter aus den Anhängen von [SzNg07] für Silizium und [KiCo14] für 4H-SiC entnommen

der Driftgebietsweite  $w$  für eine sinnvolle Driftgebietsmodifikation - bei identischem (unipolaren) Bauteilkonzept sowie gleicher maximaler Sperrfähigkeit  $U_{R,\max}$  - in Betracht kommen [DLZÖ07] [Bali08]. Eine solche Modifikation des Driftgebiets führt wiederum zu einem der Hauptargumente für die Nutzung von SiC-Bauelementen: dem geringeren spezifischen Durchlasswiderstand  $r_{on}$  bei identischen Voraussetzungen [DLZÖ07] [Bali08].

Aus Gleichung 1 [Sze02] geht durch das Einsetzen der Elementarladung  $q$ , der Dotierung  $N_D$  und der Beweglichkeit  $\mu_n$ , gemäß [Sze02] der Widerstand eines unipolaren n-dotierten Halbleiters hervor, woraus mit der Driftgebietsweite  $w$  dessen oben bereits genannter spezifischer Widerstand  $r_{on}$  (Gleichung 2) resultiert.

$$\rho = \frac{1}{q \cdot N_D \cdot \mu_n} \quad (1)$$

$$r_{on} = \frac{w}{q \cdot N_D \cdot \mu_n} \quad (2)$$

Ein negatives Merkmal von SiC sind die im Vergleich zu Silizium geringeren Werte der Beweglichkeiten  $\mu_n$  und  $\mu_p$  der Ladungsträger. Wie auch bei Silizium-Halbleiterbauelementen ist die Beweglichkeit der Elektronen  $\mu_n$  in SiC deutlich höher als die der Löcher  $\mu_p$ . Deshalb werden auch üblicherweise für Leistungshalbleiterbauelemente in SiC n- oder n-dotierte Driftgebiete beziehungsweise Grundmaterialien infolge der höheren Elektronenbeweglichkeit und des somit geringeren Durchlasswiderstands  $r_{on}$  (Gleichung 2) genutzt. Da - wie schon oben dargelegt - die Dotierung  $N_D$  stärker und die Driftgebietsweite  $w$  in SiC geringer ausfallen kann, ist die verminderte Beweglichkeit  $\mu_n$  generell kein Hindernis für die Nutzung von SiC für leistungselektronische Halbleiterbauelemente mit geringem spezifischen Durchlasswiderstand  $r_{on}$  (Gleichung 2).

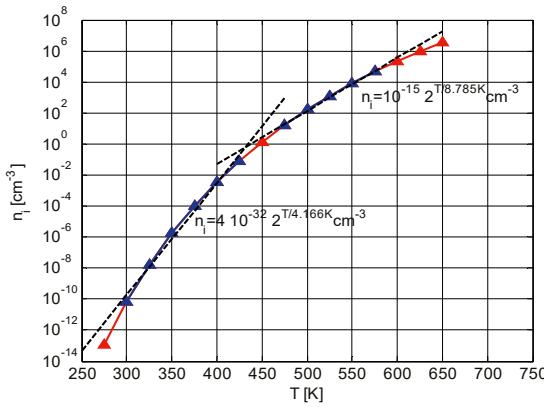

Die im Vergleich zu Silizium außerordentlich geringe intrinsische Ladungsträgerdichte  $n_i$  führt entsprechend Gleichung 3 [Sze02] zu einer ebenfalls geringen Leckstromdichte  $J_R$ , da weniger freie Ladungsträger im Halbleitermaterial verfügbar sind, die zu dieser beitragen können. Im Weiteren ist bekanntermaßen durch das sehr geringe Niveau von  $n_i$  bei Raumtemperatur davon auszugehen, dass auch bei sehr hohen Sperrsichtstemperaturen  $T_J$  im Vergleich zu Silizium-Bauelementen lediglich geringe Leckströme  $I_R$  auftreten. [Bali08]

$$J_R = J_s + J_{\text{Generation}} = q \cdot \sqrt{\frac{D_p}{\tau_p} \cdot \frac{n_i^2}{N_D} + \frac{q \cdot n_i \cdot w_{RLZ}}{\tau_g}} \quad (3)$$

Infolge der unter anderem geringen Driftgebietsweiten  $w$  und der somit geringeren spezifischen Driftgebietswiderstände  $r_{on}$  bei SiC-Halbleiterbauelementen können die SiC-Halbleiterchips wesentlich kleinere Flächen aufweisen, als im Hinblick auf  $R_{on}$  und  $U_{R,\max}$  vergleich-

bare Silizium-Halbleiterbauelemente. Die Volumina der SiC-Halbleiterbauelemente sind dementsprechend ebenfalls kleiner. Es kommt somit zu einer signifikanten Steigerung der Leistungsdichte. Aufgrund des Eintrags von Verlustleistungen im Betrieb muss das Halbleiterbauelement gekühlt beziehungsweise entwärmst werden. Das geringere Volumen von SiC-Halbleiterchips im Vergleich zu solchen aus Silizium mit gleichem Durchlasswiderstand  $R_{on}$  führt auch zu einer geringeren Wärmekapazität, wodurch sich das Halbleiterbauelement bei thermischen Transienten schneller aufheizt. Demgegenüber steht bei SiC allerdings die mehr als zweimal höhere Wärmeleitfähigkeit  $\lambda$  des Grundmaterials, welche eine bessere Kühlung des Chips zulässt.

## 2.2 Siliziumkarbid-Bauelemente

Die in diesem Abschnitt sowie den zugehörigen Unterabschnitten durchgeführte Betrachtung der Eigenschaften von Siliziumkarbid-Bauelementen sowie der gegebenenfalls notwendigen Ansteuerschaltungen beruht neben den im Text genannten Quellen anteilig auf den Veröffentlichungen [BÖRK14] [BöKa15] [BÖRK15] [BöVK15a] [BöVK15b] [BVSK15] [BVSK16].

### 2.2.1 pin-Diode

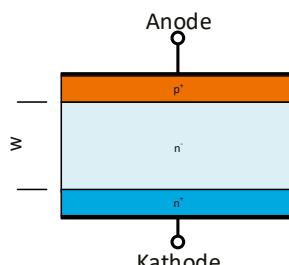

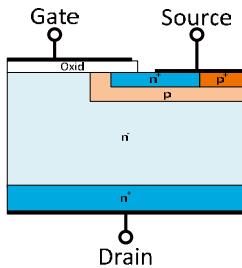

Im Sperrbetrieb der pin-Diode (Bild 2.1) kommt es infolge der Aufnahme der am pn-Übergang anliegenden Sperrspannung  $U_R$  zu einer entsprechenden Ausweitung der dort vorhandenen Raumladungszone. Es erfolgt eine vergleichsweise starke Expansion der Raumladungszone in das niedrig dotierte Driftgebiet ( $n'$ ), da das Ausmaß der Ausweitung ins jeweilige Halbleitergebiet auf der Erhaltung der Neutralität in der Raumladungszone basiert und somit dierungsabhängig ist [Reis05]. Die bekannte Begrenzung der maximal zulässigen Sperrspannung  $U_{R,max}$  durch die Driftgebiete weite  $w$  (siehe beispielsweise [Lutz12]) wird somit ersicht-

Bild 2.1: Ausschnitt aus der Struktur einer pin-Diode unter Vernachlässigung der Randabschlüsse

lich. Erste kommerzielle SiC-pin-Dioden geringer Stromtragfähigkeit sind bereits mit Sperrspannungen von  $U_{R,max} = 8 \text{ kV}$  [DB-Gene15a] beziehungsweise  $U_{R,max} = 15 \text{ kV}$  [DB-Gene15b] verfügbar.

Im Durchlassbetrieb wird das Driftgebiet der pin-Diode mit Elektronen und Löchern aus den hoch dotierten Halbleitergebieten (Bild 2.1) angereichert, wodurch ein Plasma entsteht und sich eine im Vergleich zu unipolaren Dioden hohe Leitfähigkeit einstellt. Bei SiC-pin-Dioden beträgt die Schwellenspannung der Sperrsicht geringfügig weniger als 3 V (siehe beispielsweise [DB-Gene15a] [DB-Gene15b] und Bild 5.14) und liegt somit deutlich höher als die von Silizium-pin-Dioden. Zum Erreichen einer niedrigen Durchlassspannung  $U_f$  in Abhängigkeit des Stroms  $I_f$  durch die Diode ist entsprechend eine ausreichend hohe Lebensdauer der Ladungsträger des Plasmas innerhalb des Driftgebiets der SiC-pin-Diode erforderlich. Das Plasma muss allerdings bei jedem Abschaltvorgang der Diode aus dieser extrahiert werden, wodurch eine Rückstromspitze auftritt, die sich bei einer Halbbrückenschaltung auf den Strom des in Serie zur Diode befindlichen schaltenden Transistors aufaddiert.

Problematisch bei SiC-pin-Dioden ist des Weiteren der Effekt der bipolaren Degradation, welcher zu sich ausweitenden Gebieten [LiDo11a] innerhalb der Diode führen kann [KITM17], die nicht mehr im vollen Umfang am Durchlassbetrieb teilnehmen und so die Durchlassspannung der Diode signifikant verändern [LBDH03] [Sing05] [BCHJ08]. Bedingt ist die bipolare Degradation durch die Wechselwirkung von Fehlern in der Kristallstruktur [LiDo11a] [KITM17] mit der Rekombinationsenergie von Ladungsträgern [Sing05] [BADK14] [KITM17]. Für alle SiC-Transistoren mit intrinsischen pin-Dioden ist in Bezug auf [KITM17] anzunehmen, dass sich die bipolare Degradation nicht nur auf den Diodenbetrieb auswirkt, da die gemeinsam genutzte aktive Fläche für den Transistorbetrieb ebenfalls in Mitleidenschaft gezogen wird.

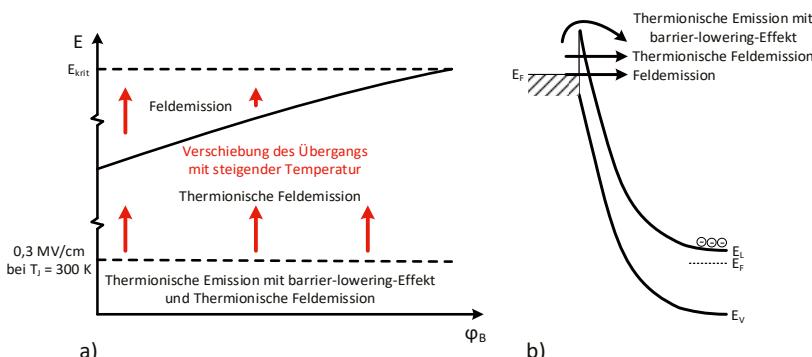

## 2.2.2 Schottky-Diode

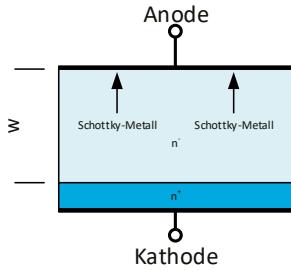

Eine Schottky-Diode besteht aus einer Struktur, bei welcher ein (Schottky)-Metall auf einen Halbleiter aufgetragen wurde (Bild 2.2). Die durch die Verbindung von Schottky-Metall und Halbleiter verursachte Schottky-Barriere  $\varphi_B$  bestimmt unter anderem die Leckstromdichte  $J_R$  durch die Sperrsicht (Gleichung 4 [HaSh02]) sowie die von der Sperrsicht verursachte Schwellenspannung [Sze02] [Lutz12]. In Gleichung 4 stellt  $A^*$  die Richardson-Konstante,  $T$  die Sperrsichttemperatur,  $\varphi_B$  die Schottky-Barriere in Elektronenvolt,  $q$  die Elementarladung,  $E$  die Feldstärke,  $\epsilon$  die Dielektrizitätskonstante und  $k_B$  die Boltzmann-Konstante dar. Ebenso wie bei der pin-Diode (Abschnitt 2.2.1) nimmt ein niedrig dotiertes Driftgebiet der Weite  $w$  (Bild 2.2) im Sperrbetrieb die Spannung  $U_R$  auf und legt somit deren maximalen Wert  $U_{R,max}$  fest.

$$J_R = A^* \cdot T^2 \cdot e^{-\frac{\varphi_B - \sqrt{\frac{q \cdot E}{4 \cdot \pi \cdot \epsilon}}}{k_B \cdot T}} \quad (4)$$

Bild 2.2: Ausschnitt aus der Struktur einer Schottky-Diode (SBD) unter Vernachlässigung der Randabschlüsse

Bild 2.3: Ausschnitt aus der Struktur einer Merged-pin-Schottky-(MPS)- beziehungsweise Junction-Barrier-Schottky-(JBS)-Diode unter Vernachlässigung der Randabschlüsse

Die in Gleichung 4 durch den Wurzelterm eingebrachte Abhängigkeit der Leckstromdichte  $J_R$  von der elektrischen Feldstärke  $E$  ist als Barrier-Lowering-Effekt bekannt [HaSh02] [KiCo14]. Offensichtlich kommt es durch das Auftreten des elektrischen Feldes  $E$  zu einer Zunahme der Leckstromdichte  $J_R$  [Lutz12] [KiCo14].

Im Gegensatz zur SiC-pin-Diode ist die SiC-Schottky-Diode ein zunächst in seiner Grundstruktur rein unipolares Halbleiterbauelement. Somit weist diese kein Plasma auf, welches beim Abschaltvorgang ausgeräumt werden muss. Lediglich die von der Sperrsichtstruktur verursachte kapazitive Ladung ist bei jedem Schaltvorgang umzuladen. Da kein Plasma vorhanden ist, kann entsprechend davon ausgegangen werden, dass bei der Schottky-Diode nach Bild 2.2 nicht mit Auswirkungen der bipolaren Degradation zu rechnen ist.

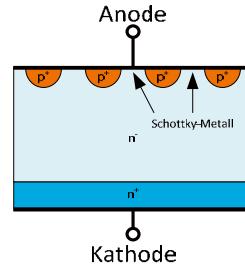

Neben der herkömmlichen Bauform, der SiC-Schottky-Barrier-Diode (SBD), gibt es noch die SiC-Merged-Pin-Schottky-(MPS)-Diode und SiC-Junction-Barrier-Schottky-(JBS)-Diode. Die MPS- und JBS-Diode unterscheiden sich bekanntlich von der SBD durch  $p^+$ -Implantationen unterhalb des Schottky-Metalls (Bild 2.3). Mit den Implantationen werden bei beiden Konzepten unterschiedliche Grundideen verfolgt: Beim MPS-Konzept soll durch die Implantationen die Stromtragfähigkeit über die Möglichkeit der Injektion erhöht werden [KiCo14], wohingegen beim JBS-Konzept die Erhöhung der Sperrfähigkeit durch eine Schirmung des Schottky-Metalls vor dem elektrischen Feld  $E$  (siehe auch Gleichung 4) im Vordergrund steht [Bali05]. Auch wenn MPS- und JBS-Dioden scheinbar formal unterschiedliche Bauelemente sind [Bali05], werden die Konzepte in dieser Arbeit aufgrund dessen, dass beide Diodentypen über  $p^+$ -Implantationen verfügen und sich nur in der Art der Ausführung selbiger unterscheiden [JSSK16], unter dem Begriff MPS-Diode verwendet.

In jedem Fall liegt durch das Einbringen von Implantationen eine Verbesserung des Sperrverhaltens vor [HeKN98] [JSSK16], wobei die Implantationen jedoch die aktive Fläche der Diode im normalen Durchlassbetrieb einschränken und sich entsprechend die Durchlassspannung  $U_F$  erhöht [HeKN98]. Beim Vergleich von Datenblättern wird jedoch offensichtlich, dass

die Durchlassspannung  $U_F$  von SiC-Schottky-Dioden (beispielsweise [DB-Infi10] [DB-Wolf16a]) deutlich unter der von intrinsischen SiC-pin-Dioden (beispielsweise [DB-Rohm15a] [DB-Wolf15a]) beziehungsweise im Bereich von Silizium-pin-Dioden (beispielsweise [DB-Ixys04]) liegt.

## 2.2.3 Bipolartransistor (BJT)

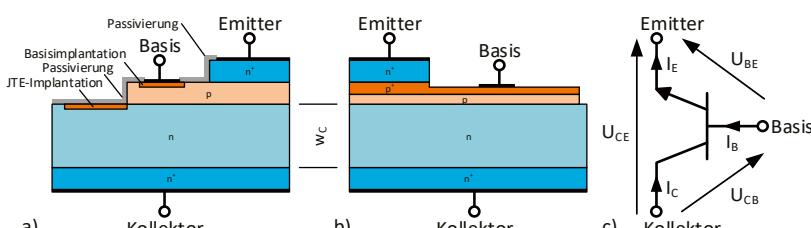

Der SiC-npn-Bipolartransistor (BJT) besteht aus einer Struktur (Bild 2.4), die durch Epitaxie gefertigt wird [GHCA06] [DLZÖ07]. Es ergeben sich zwei antiserielle Sperrsichten. Wie bei den oben genannten Dioden nimmt auch bei einem Transistor ein niedrig dotiertes Driftgebiet ( $n$ ) hier mit der Kollektorweite  $w_C$ , die Sperrspannung  $U_R$  auf (Bild 2.4a und b). So wurden zum Beispiel schon SiC-BJTs mit Sperrspannungen von  $U_{CE,max} = 21$  kV gefertigt, wie aus der Veröffentlichung [MONK12] hervorgeht.

Aufgrund der antiseriellen Sperrsichten nimmt die Durchlassspannung  $U_{CE}$  des BJT gemäß der Gleichung  $U_{CE} - U_{BE} - U_{CB} = 0$  (siehe auch Bild 2.4c) im Sättigungsbetrieb einen Wert an, der deutlich unter den Absolutwerten der einzelnen Sperrsichten von circa 3 V liegt [DLZÖ07].

Die charakteristische Größe eines Bipolartransistors ist die erreichbare Verstärkung  $B$  beziehungsweise  $h_{FE}$ , welche sich aus dem Transportfaktor  $\alpha_T$  und der Emittereffizienz  $\gamma$  beziehungsweise dem Verhältnis des Kollektorstroms  $I_C$  zum Basisstrom  $I_B$  zusammensetzt (Gleichung 5 [SzNg07], siehe auch Bild 2.4c).

$$B = h_{FE} = \frac{I_C}{I_B} = \frac{\gamma \cdot \alpha_T}{1 - \gamma \cdot \alpha_T} \quad (5)$$

Bei der Herstellung des SiC-BJTs unbeabsichtigt in das Halbleitermaterial eingebrachte Störstellen können sich in einem signifikanten Maße negativ auf die Verstärkung  $B$  auswirken, da diese zu einer Zunahme der Rekombination innerhalb des BTJs führen [DLZÖ07]. Häufig werden in der Literatur parasitäre Rekombinationszentren zwischen den Epitaxieschichten

**Bild 2.4: Struktur einer Halbzelle eines npn-Bipolartransistors in Siliziumkarbid a) gemäß [LiDo11b] ähnlich [RASP01] mit Implantationen und b) gemäß [ZLAB08] als implantationsfreie Struktur sowie c) das Transistor-Symbol mit Spannungen und Strömen**

[GHXZ06], an der Oberfläche [DLZÖ07] [GBDZ11] sowie in der Umgebung der p<sup>+</sup>-Implantationen angegeben [ZLAB08] [GLDB08] [GBDZ11]. Zur Vermeidung von Rekombinationszentren, die durch die p<sup>+</sup>-Basisimplantationen verursacht werden, wurde die implantationsfreie Struktur nach Bild 2.4b in [ZLAB08] gezeigt.

Bei SiC-BJTs mit einer Sperrfähigkeit von  $U_{R,max} = 1,2$  kV ist trotz der eigentlich bipolartransistortypischen Eigenschaften keine nennenswerte Leitfähigkeitsmodulation des Driftgebiets vorhanden [LiDo11b] [SSLD12]. Dieses ist aufgrund des schmalen Driftgebiets eines 1,2 kV SiC-BJTs [DLZÖ07] sowie der hohen Dotierung des selbigen [GHXZ06] [DLZK10] auch nicht zielführend, da hierdurch, wie aus den genannten Quellen hervorgeht, ein ohnehin schon ausreichend niedriger Durchlasswiderstand bedingt ist.

Die Leitfähigkeitsmodulation ist des Weiteren auch bei SiC-BJTs ein kritischer Faktor, da diese hier ebenfalls (siehe auch Abschnitt 2.2.1) zur bipolaren Degradation führen kann [ZBHC09] [LiDo11a] [LiDo11b]. Es wurde jedoch in der Literatur [BADK14] die Nutzung eines optischen Verfahrens beschrieben, um SiC-BJTs mit Kristallfehlern, die potentiell zur bipolaren Degradation führen können, auszusortieren und somit in Bezug auf das Durchlassverhalten SiC-BJTs mit langfristig stabilen Eigenschaften zu gewährleisten.

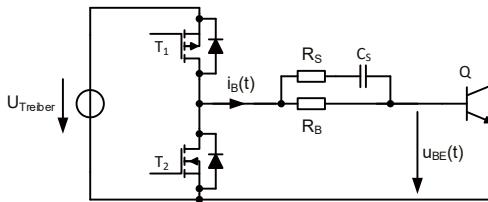

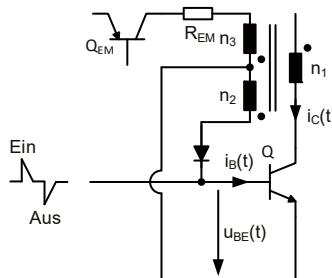

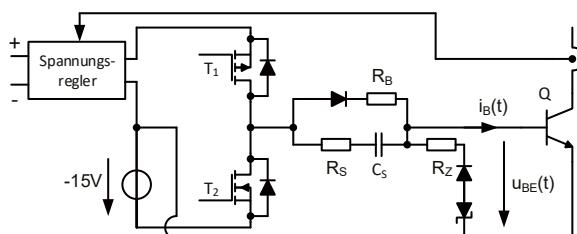

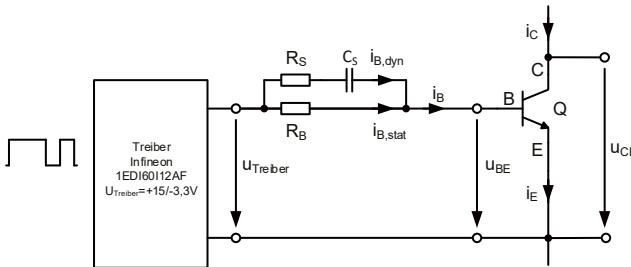

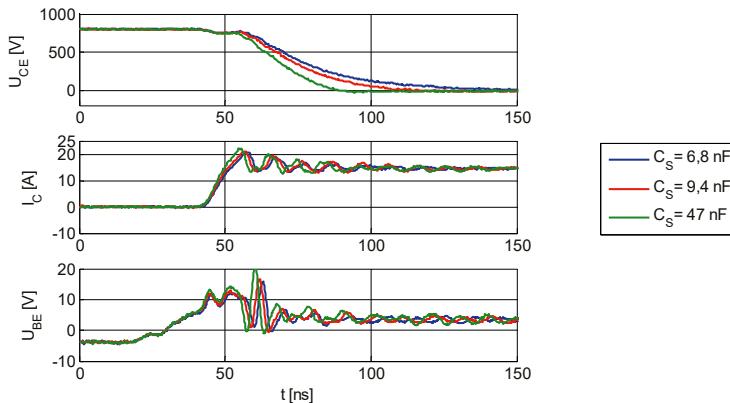

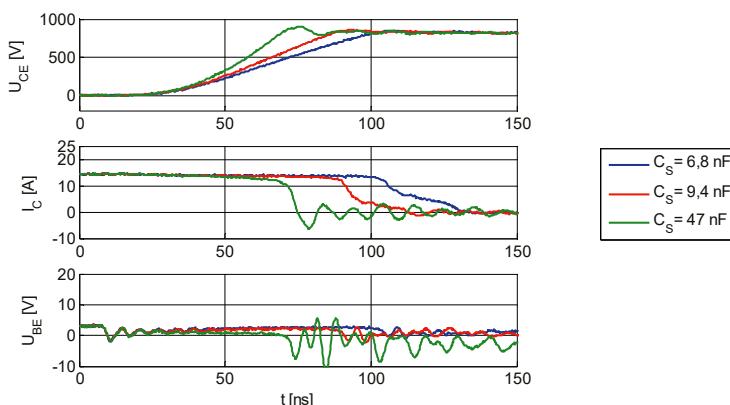

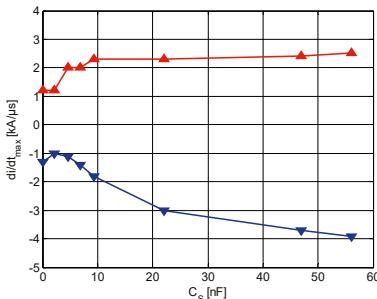

Für die Ansteuerung eines (SiC)-BJTs ist ein leistungsfähiger Treiber unabdingbar, da im Durchlassbetrieb ein permanenter Strom  $I_B$  von der Basis in den Emitter (Bild 2.4c) aufrecht-erhalten [DLZÖ07] beziehungsweise eine für Transistoren erhebliche Ansteuerleistung zuge-führt werden muss [RTPN12] (siehe auch nachfolgende Abschnitte 2.2.4 und 2.2.5). Da wie oben beschrieben beim 1,2 kV SiC-BJT keine nennenswerte Leitfähigkeitsmodulation auftritt und somit kaum Plasma im n-Gebiet vorhanden ist, hat auch keine Beschaltung durch eine Antisättigungsschaltung (siehe [Thom79]) zu erfolgen, um den Sättigungsbereich zu meiden und ein schnelles Abschalten zu ermöglichen [LiDo11b] [RTPN12]. Die Eingangskapazität des SiC-BJTs, im Speziellen die Basis-Kollektor-Teilkapazität  $C_{BC}$ , sollte beim Schalten in einem möglichst kurzen Zeitraum umgeladen werden, so dass sich schnelle Schaltvorgänge einstellen [DLZK10] [LiDo11b]. Typischerweise wird hierfür ein Treiber mit Speed-Up-Kondensator [DLZK10] verwendet (Bild 2.5). Dieser führt dem BJT über den Kondensator  $C_S$  bei jedem Schaltvorgang einen kurzzeitigen erhöhten Basis-Strom  $i_B$  zu [DLZK10] [LiDo11b]. Nachteilig wirkt sich im Hinblick auf SiC-BJTs mit ihrem potentiell im Vergleich zum Silizium-BJT schnelleren Schaltverhalten die Zeitkonstante  $\tau_{RC}$  des RC-Impedanznetzwerks aus, da die Kapazität  $C_S$  über  $R_S$  und  $R_B$  umgeladen werden muss [RTPN12].

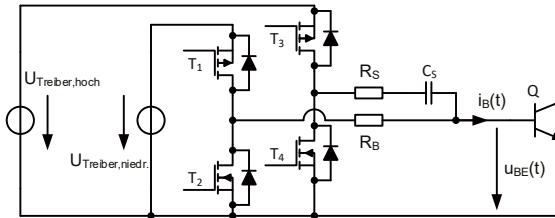

Neben dem oben genannten Treiber gibt es noch diverse weitere Treiberkonzepte, mit welchen eine Optimierung in Bezug auf die Ansteuerleistung angestrebt wird: Beispiele hierfür sind ein zweistufiger Treiber mit RC-Impedanznetzwerk, welcher durch eine hohe Ansteuer-spannung einen kurzzeitigen Pulsstrom über das RC-Impedanznetzwerk liefert und im Durch-lassfall lediglich eine niedrige Ansteuerspannung ausgibt (Bild 2.6) [RTPN12], ein einstufiger

Bild 2.5: Typische Ansteuerung mit RC-Impedanznetzwerk; gemäß [DLZK10] oder [Thom79] (mit einem leicht anderen Impedanznetzwerk)

Bild 2.6: Zweistufige Treiberschaltung mit RC-Impedanznetzwerk, welche für den kurzzeitigen Pulssstrom über eine hohe Ansteuerspannung und für den statischen Durchlassstrom über eine niedrige Ansteuerspannung verfügt; gemäß [RTPN12]

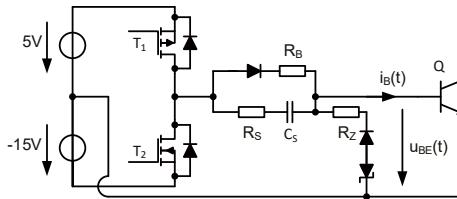

Bild 2.7: Ansteuerung mit RC-Impedanznetzwerk und niedriger positiver Ansteuerspannung für den statischen Durchlassbetrieb; gemäß [FHLD14]

Bild 2.8: Treiberschaltung, welche beim Einschalten als Stromquelle agiert und eine niedrige statische Ansteuerspannung aufweist; gemäß [RPNZ12]

Treiber mit einem ebenfalls kurzzeitig beim Schaltvorgang erhöhten Basisstrom  $i_B$ , aber einer gleichzeitig niedrigen positiven Ansteuerspannung (Bild 2.7) [FHLD14] sowie ein Treiber, wel-

Bild 2.9: Ansteuerschaltung mit zum Laststrom  $i_c$  proportionalem Basisstrom  $i_B$  für den statischen Durchlassbetrieb; gemäß [Thom79]

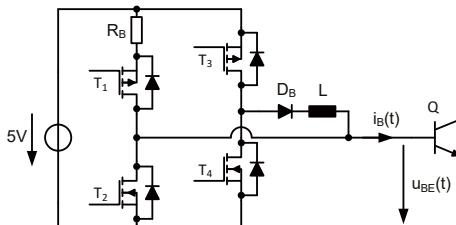

Bild 2.10: Treiberschaltung mit RC-Impedanznetzwerk und zum Laststrom  $i_c$  proportionaler positiver Ansteuerspannung für den statischen Durchlassbetrieb; gemäß [FHLD14]

cher beim Einschalten wie eine Stromquelle wirkt und ebenfalls eine geringe statische Ansteuerspannung aufweist (Bild 2.8) [RPNZ12]. Ebenso existieren Treiberkonzepte, bei welchen der Basisstrom  $i_B$  in einem definierten Verhältnis zum Kollektorstrom  $i_c$  vorgegeben wird, um die Ansteuerleistung zu vermindern [Thom79]: Dieses sind zum einen Treiber, welche einen proportionalen Strom  $i_B$  über einen Transformator aus dem Lastkreis auskoppeln (Bild 2.9) und in den Ansteuerkreis speisen [Thom79] [RTPN12]. Zum anderen sind dies aber auch Treiber mit Spannungswandlern (Bild 2.10), die eine zum Laststrom proportionale positive Ansteuerspannung  $U_{\text{Treiber}}$  liefern [FHLD14].

## 2.2.4 Sperrsichtfeldeffekttransistor (JFET)

Der n-Kanal-Sperrsichtfeldeffekttransistor (JFET) ist ein Transistor (Bild 2.11 bis Bild 2.13), der durch die Einschnürung des Kanals mittels der Raumladungszonen der vorhandenen Sperrsichten gesteuert wird. Im Gegensatz zum BJT, der ebenfalls durch eine Sperrsicht gesteuert wird, ist beim JFET jedoch kein Stromfluss durch die Sperrsichten notwendig. Die Steuerung des JFET erfolgt über die Ausdehnung der Raumladungszonen. Hierfür ist bekanntermaßen nur eine Potentialdifferenz über diese anzulegen. Die erforderliche Treiberleistung für den JFET ist somit gegenüber dem BJT stark reduziert, da nur die für die Umladung

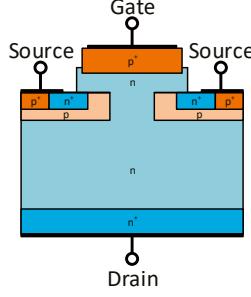

Bild 2.11: Ausschnitt aus der Struktur eines n-Kanal JFETs in Siliziumkarbid; gemäß [SRKB10] ähnlich [BhBL15]

Bild 2.12: Ausschnitt aus der Struktur eines n-Kanal JFETs in Siliziumkarbid; gemäß [GCFH11]

Bild 2.13: Ausschnitt aus der Struktur eines n-Kanal JEFTs in Siliziumkarbid; gemäß [SiKi11]

der Sperrsichten notwendige Treiberleistung bereitgestellt werden muss (siehe auch Abschnitt 2.2.3).

Den SiC-JEFT gab beziehungsweise gibt es von verschiedenen Herstellern mit normally-off- (selbstsperrend) und normally-on- (selbstleitend) Struktur. Der Hersteller SemiSouth Laboratories, Inc. hatte hierbei eine normally-off-Struktur [SRKB10] [GCFH11] bevorzugt (Bild 2.11 und Bild 2.12), die im Hinblick auf eine erstrebenswerte intrinsische Sicherheit von Spannung zwischen Kreisumrichtern zweckmäßig ist [Knei98]. Nach Grekov et al. [GCFH11] sind die beiden Merkmale, die den normally-off- vom normally-on-SiC-JFET unterscheiden, die Kanalweite und -dotierung. Die Abhängigkeit der normally-off- beziehungsweise normally-on-Kanaleigenschaft von der Dotierung und der Weite des n-Kanalgebiets lässt sich über die Abhängigkeit einer Raumladungszone von der Dotierung verstehen: Die zum Sperren notwendigen Raumladungszonen weiten sich umso stärker in ein Halbleitergebiet aus, desto niedriger dieses dotiert ist (siehe auch Abschnitt 2.2.1). Damit der normally-off-JFET durch die Einschnürung des Kanals vollständig sperrt, ist demzufolge im Vergleich zum normally-on-JFET eine

niedrigere Dotierung des n-Kanalgebiets bei gleicher Weite des Kanals oder eine geringere Kanalweite bei gleicher Dotierung erforderlich. Bhalla et al. zeigten in der Veröffentlichung [BLAD13], dass normally-off-SiC-JFETs immer einen höheren spezifischen Durchlasswiderstand als ihre normally-on-Gegenstücke der gleichen Bauteilgeneration haben werden. Da die Kanaldotierung bei der Berechnung des spezifischen Widerstands in den Teiler eingeht (siehe beispielsweise [GCFH11] [KiCo14]), muss entsprechend ein höherer spezifischer Widerstand beim normally-off- im Vergleich zum normally-on-SiC-JFET bei ansonsten identischen Eigenschaften gegeben sein.

Die Hersteller United Silicon Carbide, inc. (USCI) und Infineon Technologies AG hingegen produzieren beziehungsweise produzierten normally-on-SiC-JFETs, jedoch mit unterschiedlichen Strukturen. Während USCI dieselbe Struktur wie SemiSouth verwendet [BhBL15] (Bild 2.11), nutzte Infineon eine Struktur mit planarem Kanal, die zudem über eine intrinsische pin-Diode als Freilaufdiode verfügt [SiKi11] (Bild 2.13). Nachteilig bei der von USCI und vormals ebenfalls von SemiSouth verwendeten Struktur (Bild 2.11) soll entsprechend Siemieniec et al. [SiKi11] die strukturell bedingt große Gate-Drain-Kapazität  $C_{GD}$  sein, die sich negativ auf das Schaltverhalten des JFETs als Einzelschalter auswirkt. In der Veröffentlichung von Sheridan et al. [SRKB10] wurde für den normally-off-JFET von SemiSouth auch eine zweistufige Ansteuerung mit einem zusätzlichen kurzeitigen Strompuls beim Einschaltvorgang empfohlen, um den normally-off-SiC-JFET (Bild 2.11) möglichst schnell aufzusteuern.

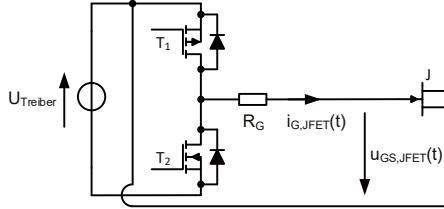

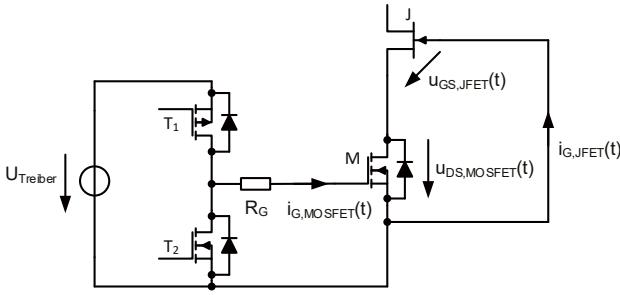

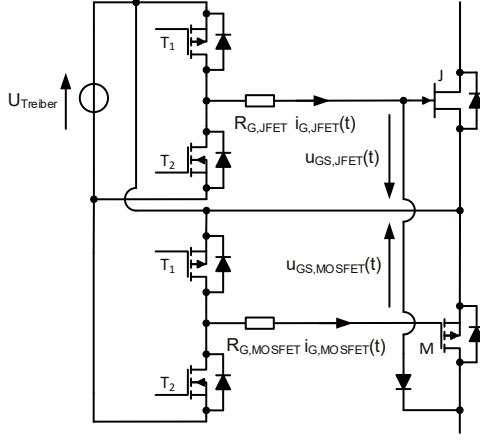

Falls der normally-on-JFET als einzelner Transistor betrieben wird (Bild 2.14), muss im Sperrbetrieb typischerweise eine Ansteuerspannung  $U_{Treiber}$  im Bereich von  $U_{Treiber} = -15 \text{ V}$  [DB-Unit00] bis  $U_{Treiber} = -19,5 \text{ V}$  [DB-Infi13a] an diesen aktiv angelegt werden. Normally-on-SiC-JFETs werden aber häufig in Kaskoden mit niedersperrenden normally-off-Silizium-MOSFETs betrieben, um diesen ein normally-off-Verhalten aufzuzwingen [SiKi11] [BBDD12] [Bend16]. Hierbei gibt es zwei unterschiedliche Konzepte: Entweder kann lediglich der normally-off-Silizium-MOSFET aktiv angesteuert werden, wobei der MOSFET beim Abschalten eine negative Spannung  $u_{GS,JFET}$  zwischen Gate und Source des normally-on-JFET erzeugt [Bend16] (Bild 2.15) oder es wird nur der normally-on-SiC-JFET moduliert angesteuert und der normally-off-Silizium-MOSFET agiert im Fall einer wegfallenden Versorgungsspannung als Sicherheitsglied in der Ansteuerung [SiKi11] [BBDD12] (Bild 2.16).

Bild 2.14: Ansteuerung eines normally-on-SiC-JFETs

Bild 2.15: Ansteuerung eines normally-on-SiC-JFETs in einer Kaskode zur Erlangung des gewünschten normally-off-Verhaltens; gemäß [Bend16]

Bild 2.16: Ansteuerung eines normally-on-SiC-JFETs in einer Kaskode, in welcher der Silizium-MOSFET nicht moduliert geschaltet wird; gemäß [BBDD12]

Die Struktur des SiC-JFETs, wie er von USCi hergestellt wird, weist zwar keine Freilaufdiode auf, jedoch ist auch keine erforderlich, da der SiC-JFET in einer Kaskode, über die an der Freilaufdiode des Silizium-MOSFETs anliegende Spannung  $u_F$ , im Freilauffall automatisch aufgesteuert wird [Bend16]. Da keine Freilaufdiode notwendig beziehungsweise vorhanden ist, entfällt entsprechend die Problematik der bipolaren Degradation der pin-Struktur einer intrinsischen SiC-Freilaufdiode gänzlich (siehe auch Abschnitt 2.2.1).

## 2.2.5 Metall-Oxid-Halbleiter-Feldeffekttransistor (MOSFET)

Der n-Kanal-Metall-Oxid-Halbleiter-Feldeffekttransistor (MOSFET) ist ein Transistor, der über einen MOS-Kondensator beziehungsweise durch den daraus herrührenden n-leitenden

Kanal gesteuert wird. Im Gegensatz zum BJT oder JFET findet also keine Steuerung des Transistors über eine oder mehrere Sperrsichten statt. Im MOS-Kondensator bildet ein Oxid (Gate-Oxid) das trennende Dielektrikum, unter welchem der Kanal des Transistors liegt (Bild 2.17). Durch das Dielektrikum fließt im Normalbetrieb ausschließlich ein sehr geringer Leckstrom beziehungsweise der bei einer Umladung der Eingangskapazität  $C_{iss}$  infolge einer Umschaltung des MOSFETs auftretende Gate-Strom  $i_G$ . Im Gegensatz zum BJT begründet sich hieraus wie beim JFET auch der Vorteil einer deutlich geringeren Ansteuerleistung (siehe auch Abschnitt 2.2.3).

Alle SiC-MOSFETs haben, bedingt durch ihre zugrundeliegenden Strukturen (Bild 2.17 und Bild 2.18), eine unvermeidbare intrinsische pin-Freilaufdiode mit den für diese Bauteilart typischen Eigenschaften (siehe Abschnitt 2.2.1). Beim SiC-MOSFET kann deshalb, wie bei SiC-pin-Dioden auch, aufgrund einer Nutzung der intrinsischen pin-Freilaufdioden die bipolare Degradation eintreten [KITM17].

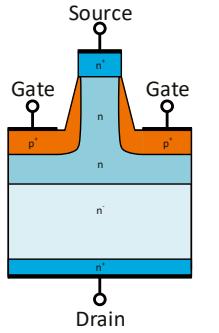

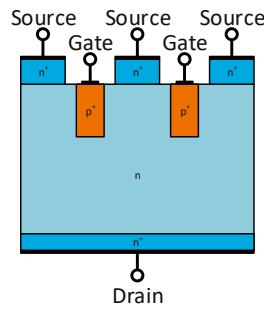

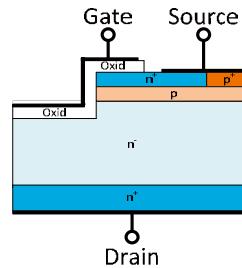

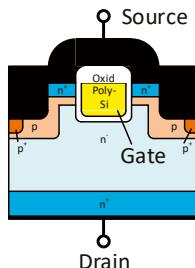

Für einen vertikalen n-Kanal-Leistungs-SiC-MOSFET gibt es, wie auch in Silizium, zwei grundlegende Strukturen: Den MOSFET mit einem planaren Kanal (Bild 2.17, D-MOSFET) und den Trench-MOSFET mit einem vertikalen Kanal (Bild 2.18, U-MOSFET). Der Kanal wird beim

Bild 2.17: Struktur einer Halbzelle eines n-Kanal D-MOSFETs in Siliziumkarbid; gemäß [KiCo14]

Bild 2.18: Struktur einer Halbzelle eines n-Kanal U-MOSFETs in Siliziumkarbid; gemäß [KiCo14]

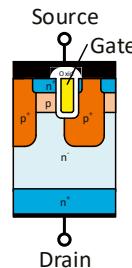

Bild 2.19: Double-Trench-Struktur von Rohm; gemäß [KNMN16]

Bild 2.20: Trench-Struktur von Infineon; gemäß [PSAB17]

SiC-U-MOSFET in die a- beziehungsweise <11-20>-Ebene des Kristalls gelegt, um eine bestmögliche Kanaloberfläche zu erhalten [KiYN13] [LAXI13] [HeDP16] [PSAB17]. Beim SiC-U-MOSFET ergibt sich daraus gegenüber dem SiC-D-MOSFET der strukturell bedingte Vorteil einer höheren Beweglichkeit  $\mu_n^*$  im vertikalen Kanal und daraus resultierend ein geringerer Kanalwiderstand [KiYN13] [HeDP16] [PSAB17].

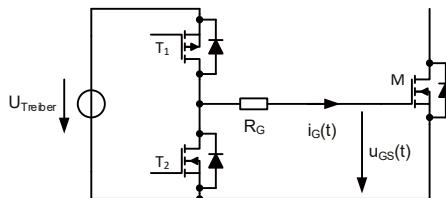

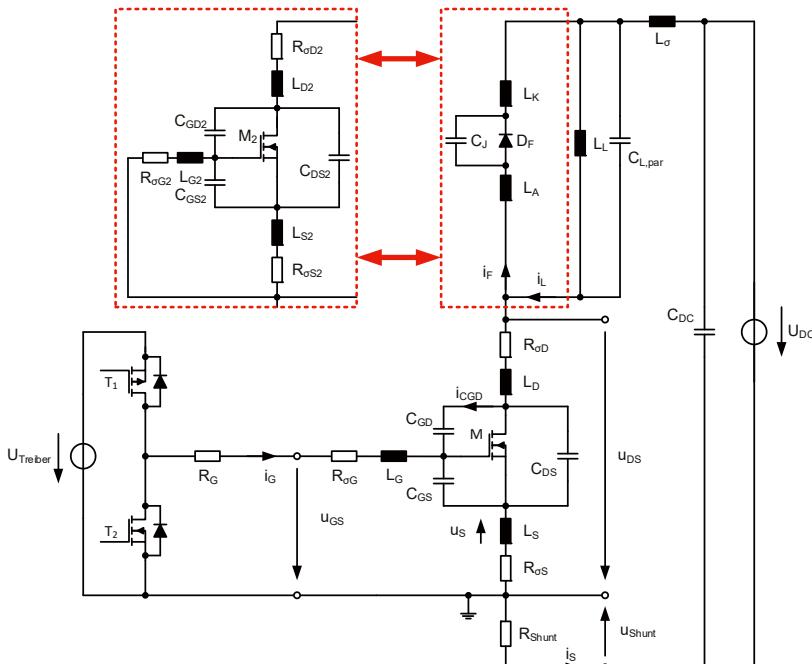

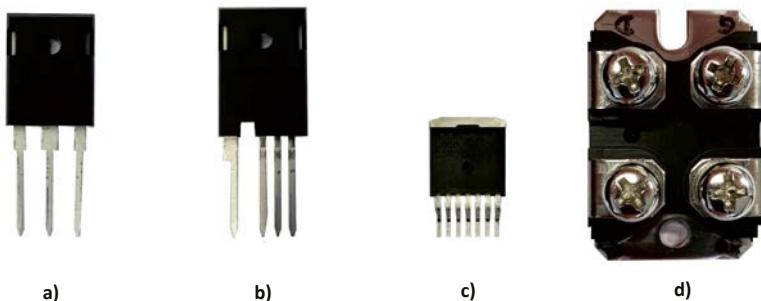

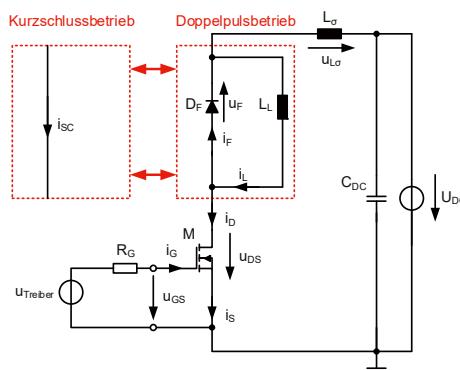

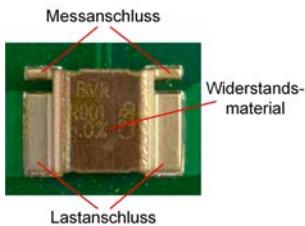

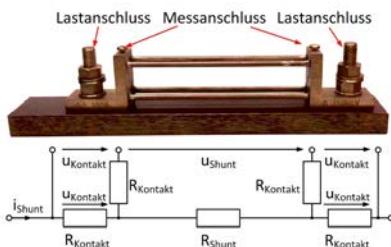

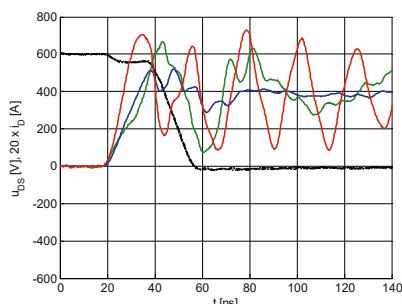

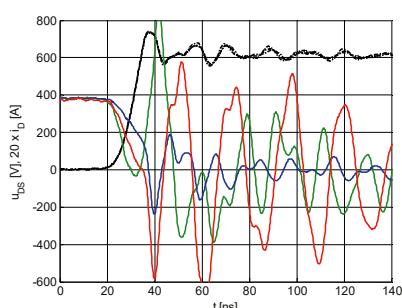

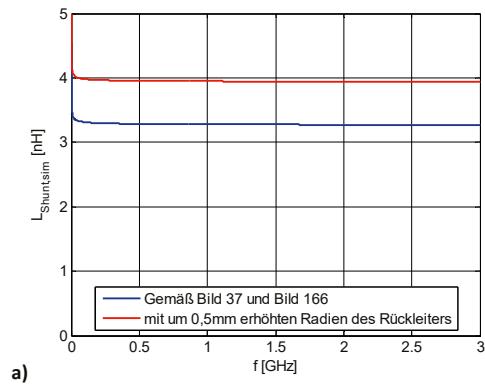

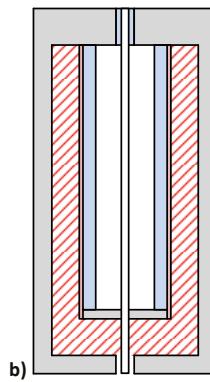

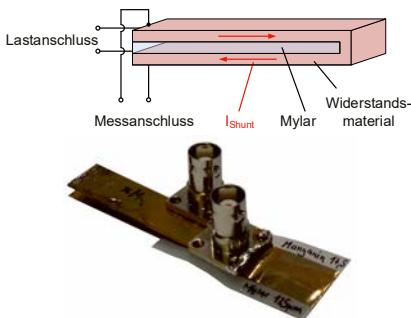

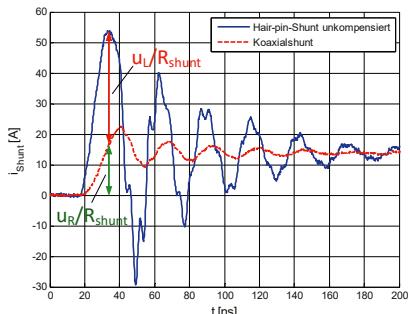

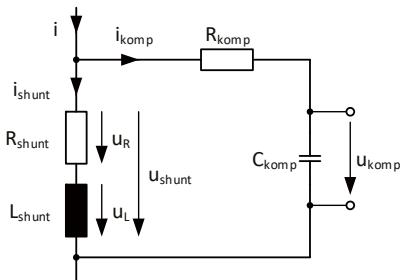

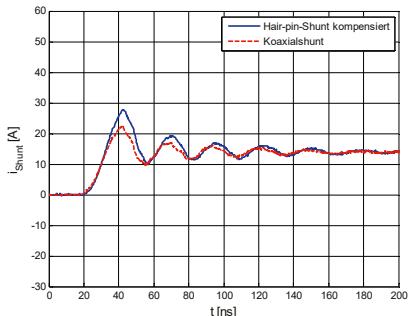

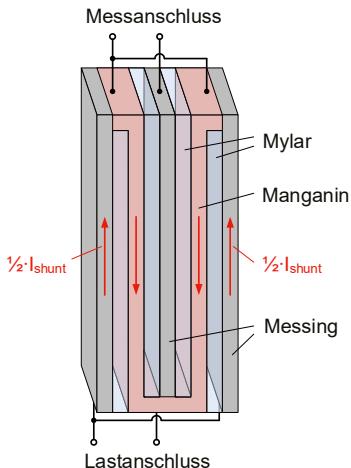

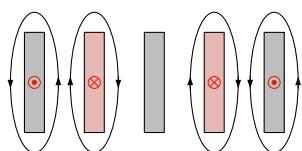

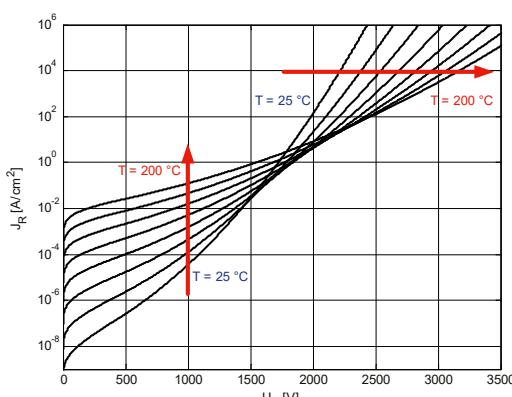

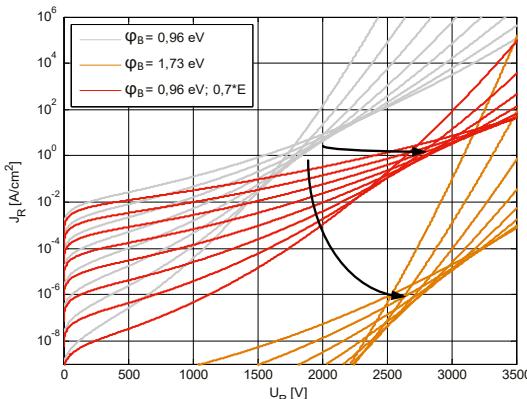

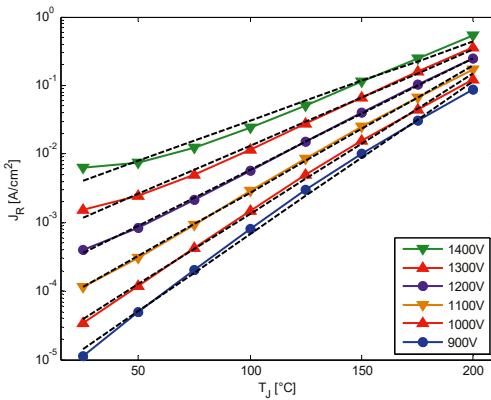

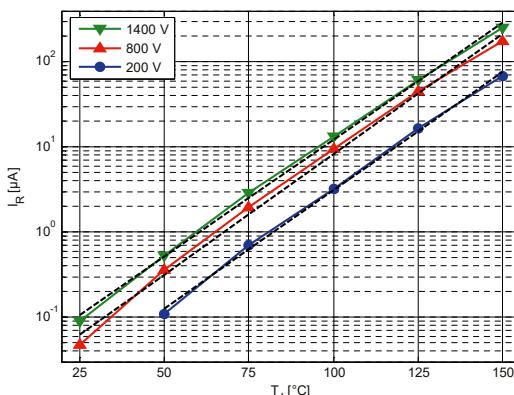

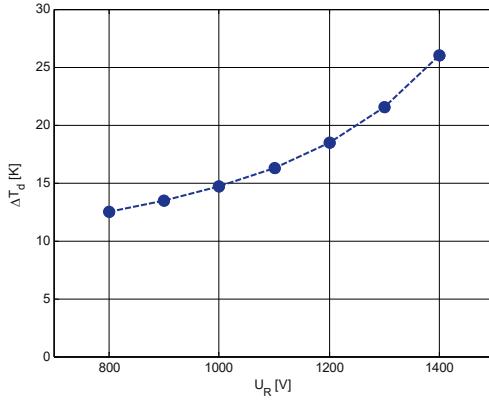

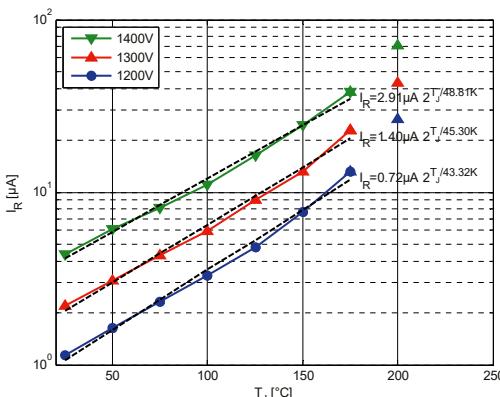

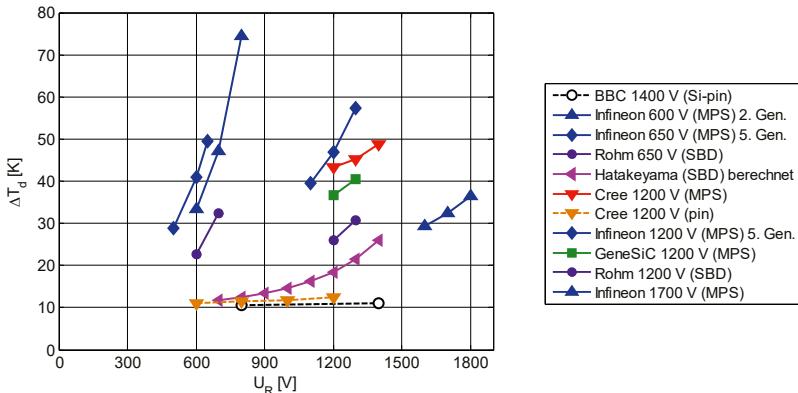

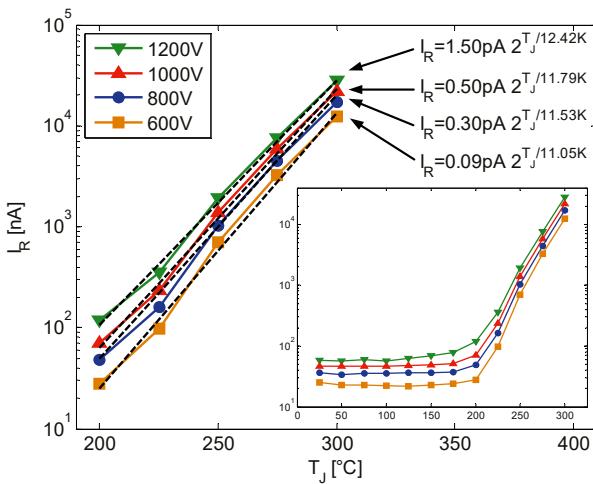

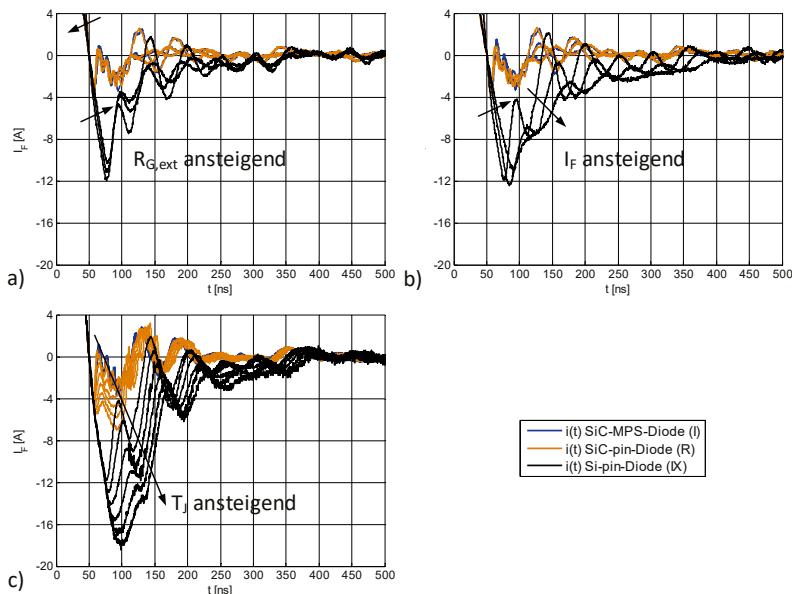

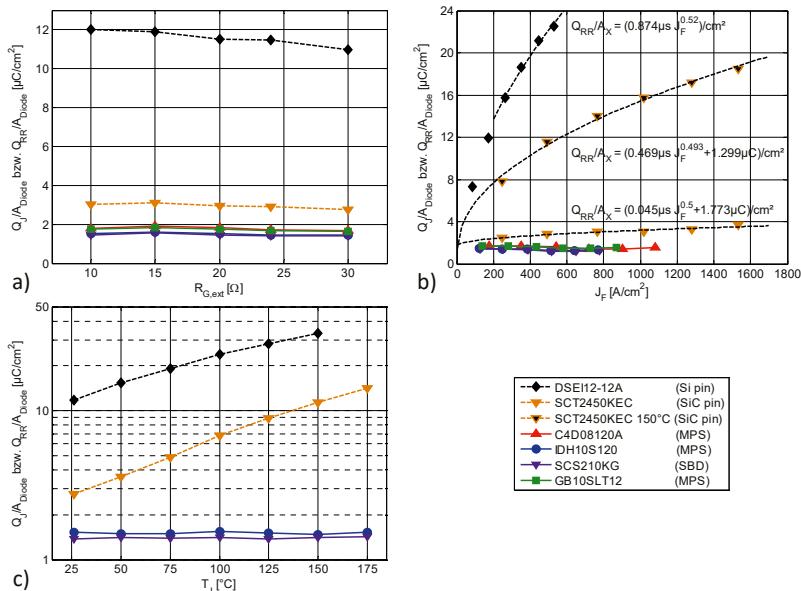

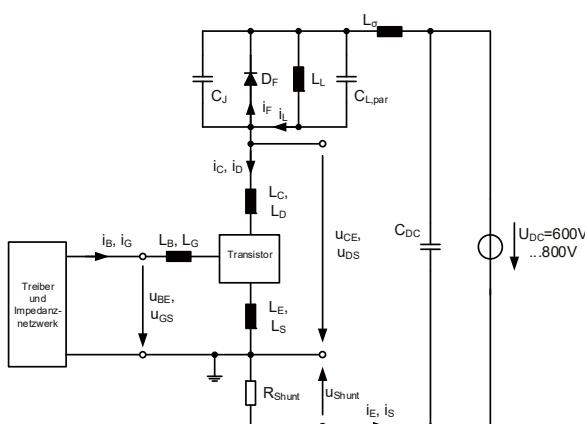

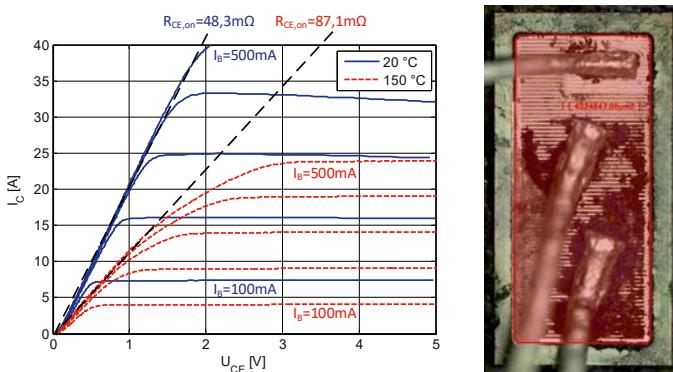

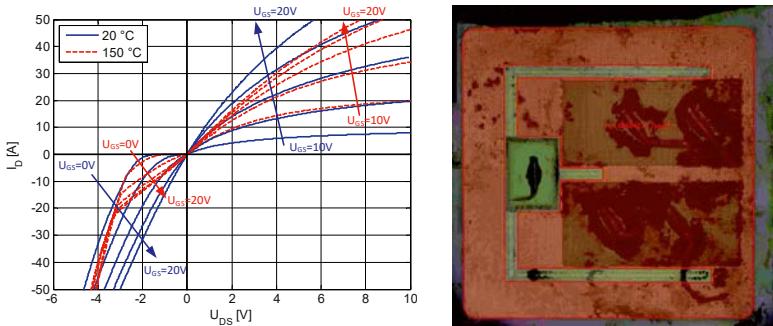

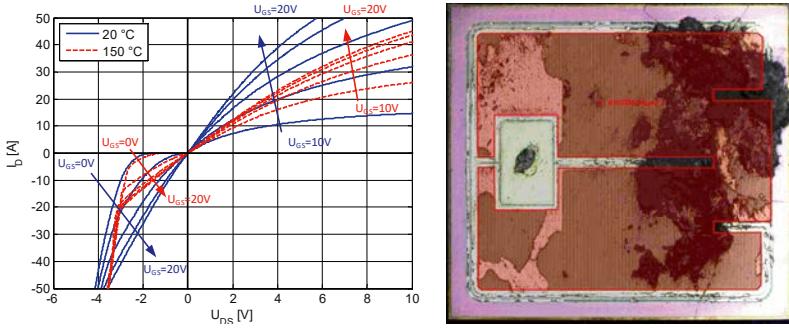

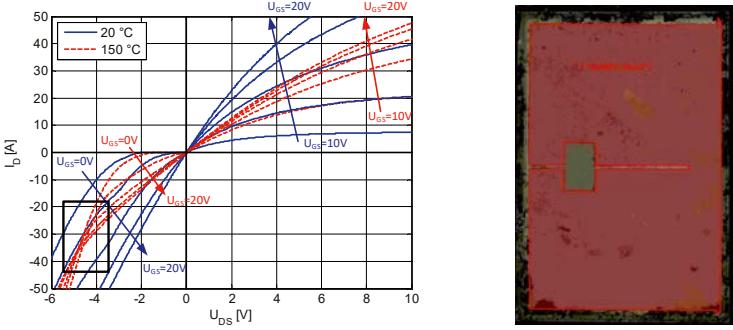

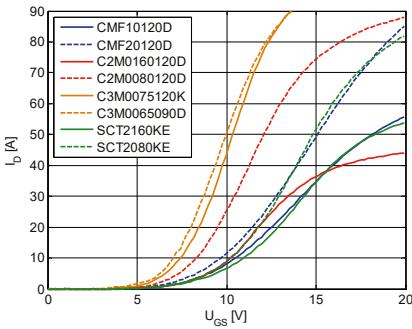

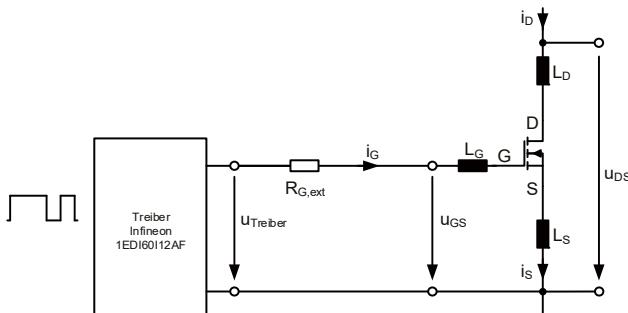

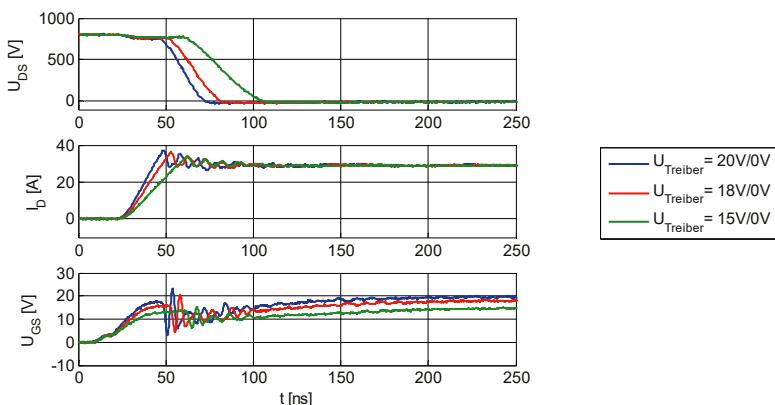

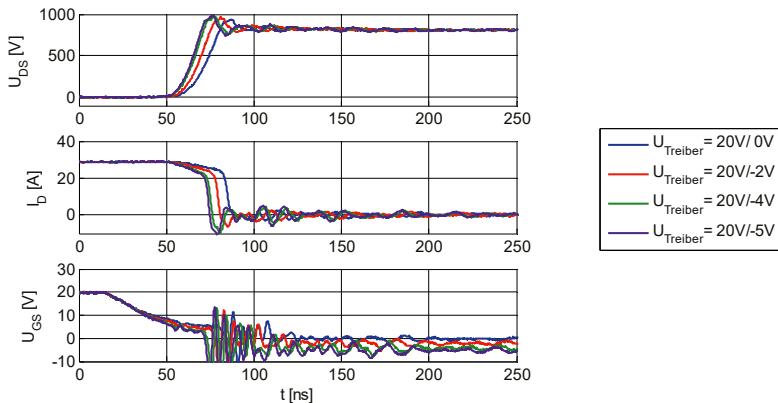

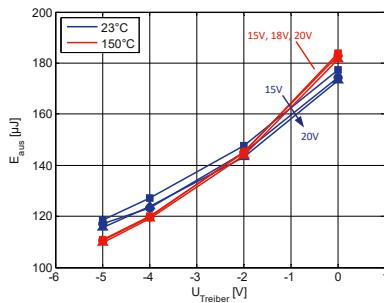

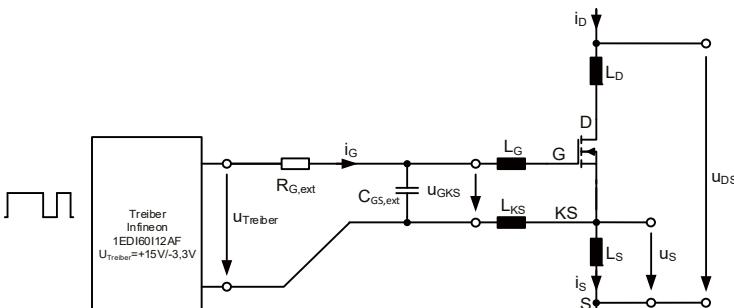

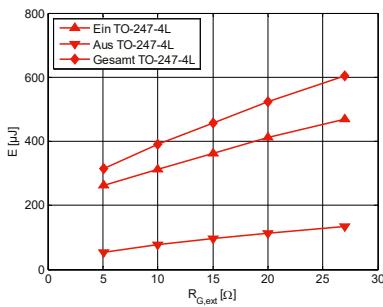

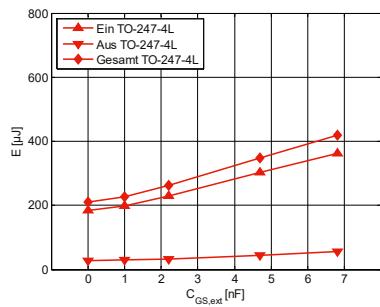

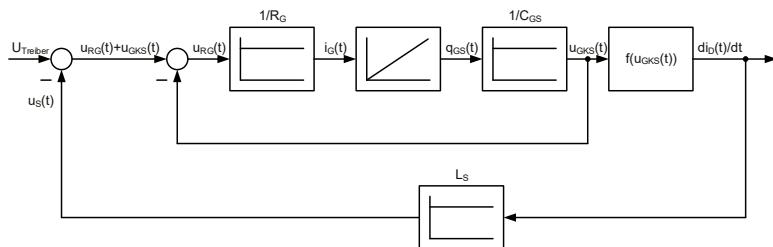

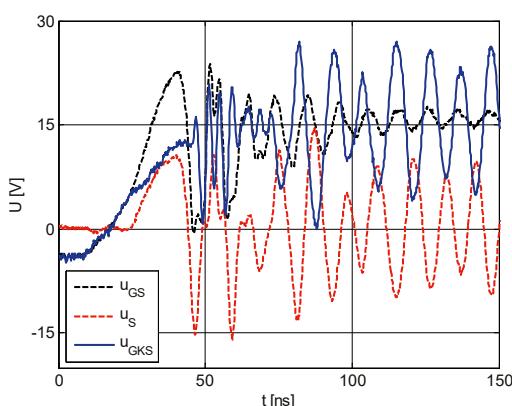

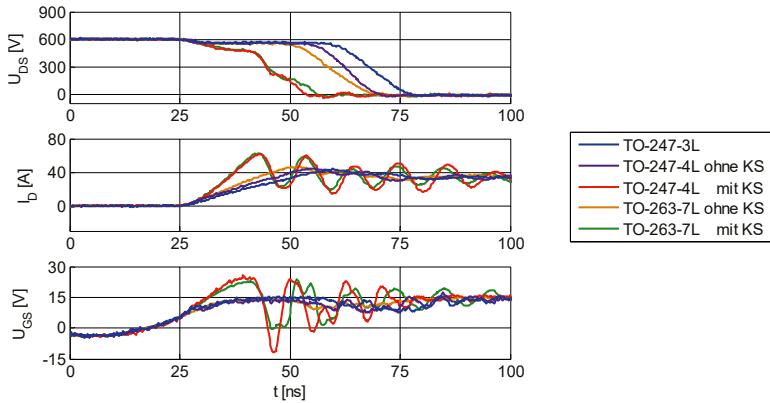

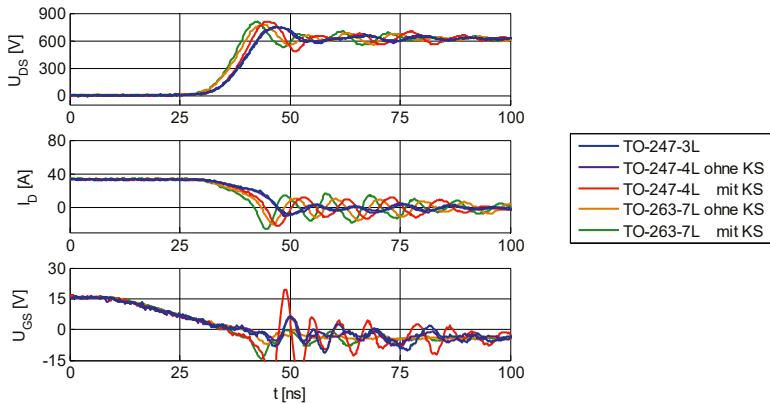

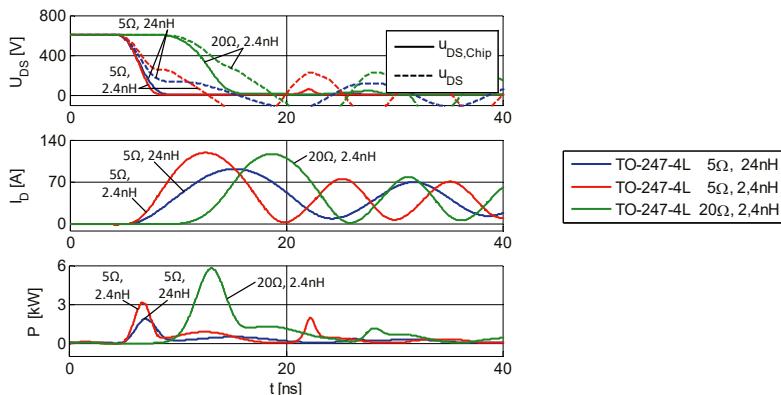

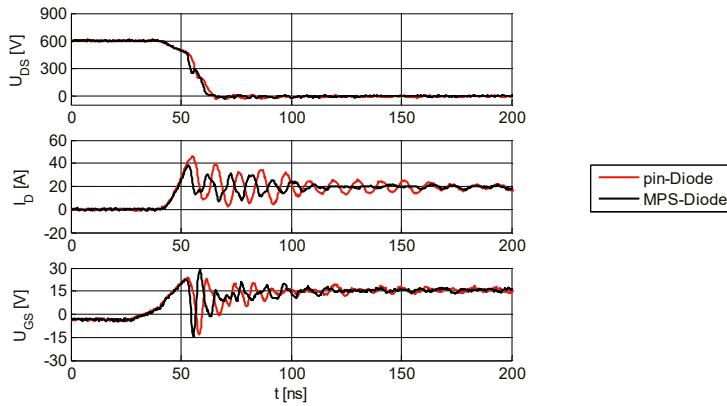

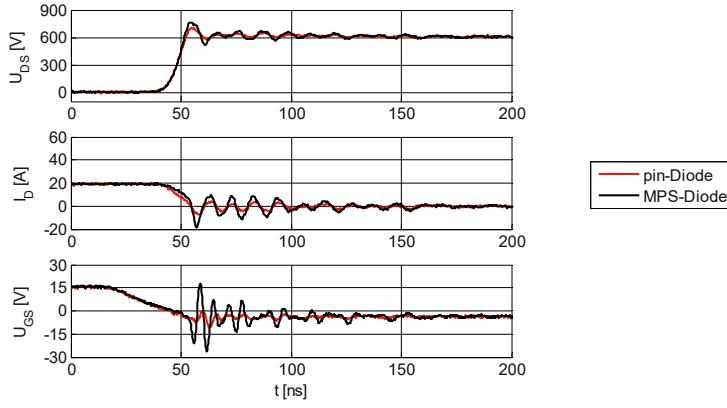

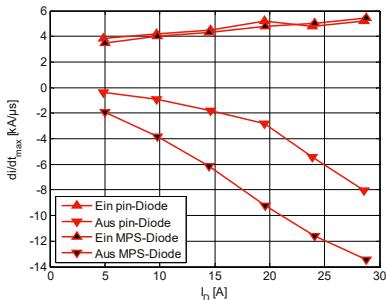

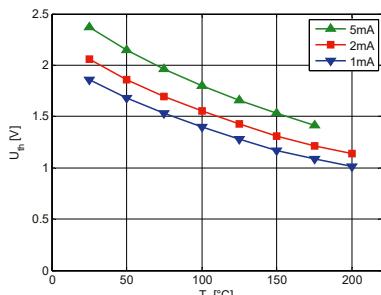

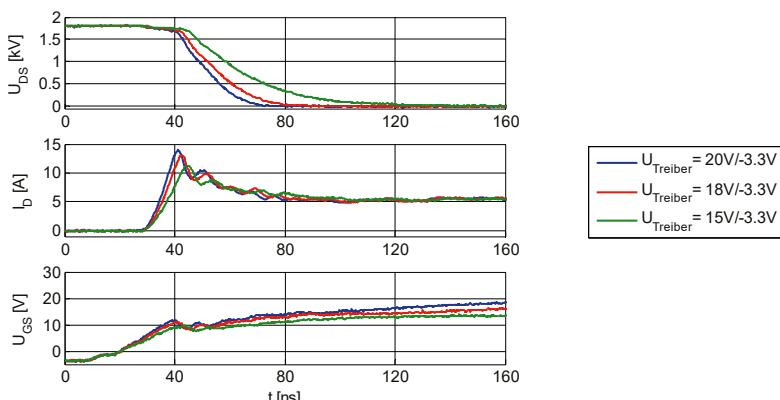

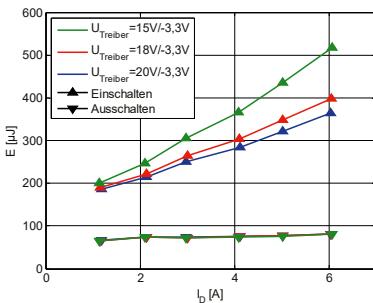

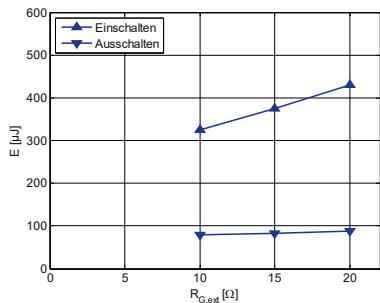

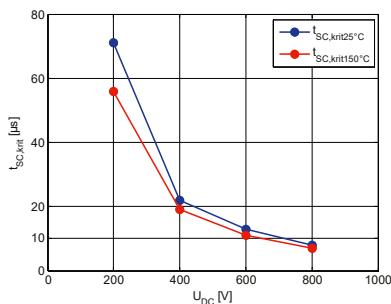

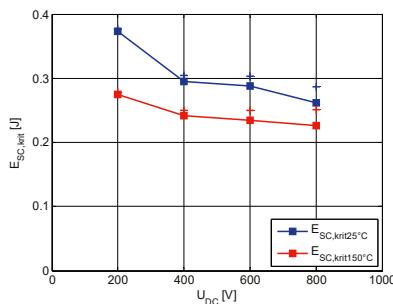

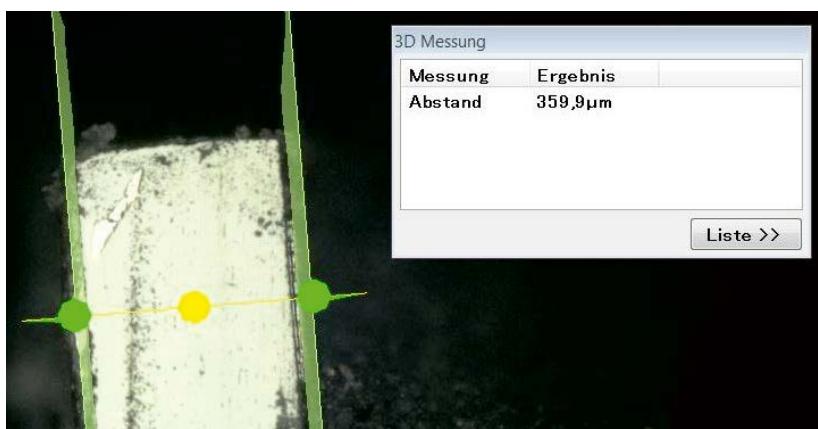

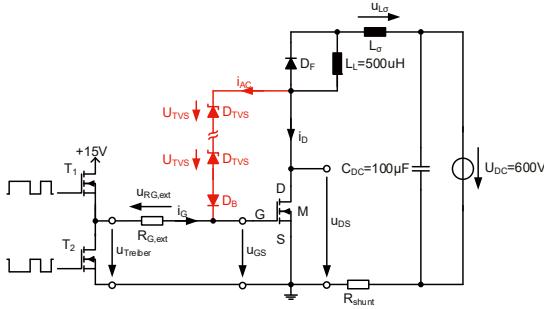

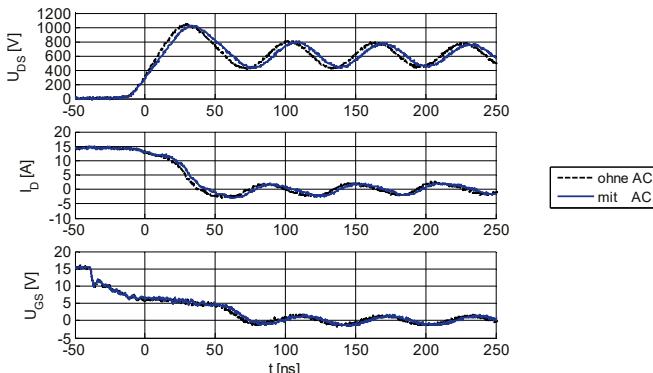

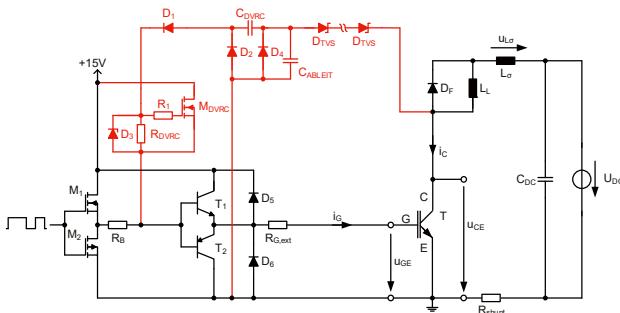

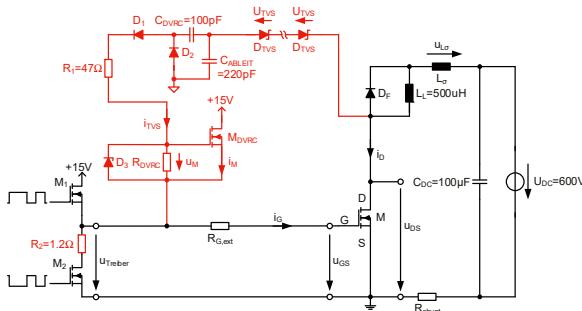

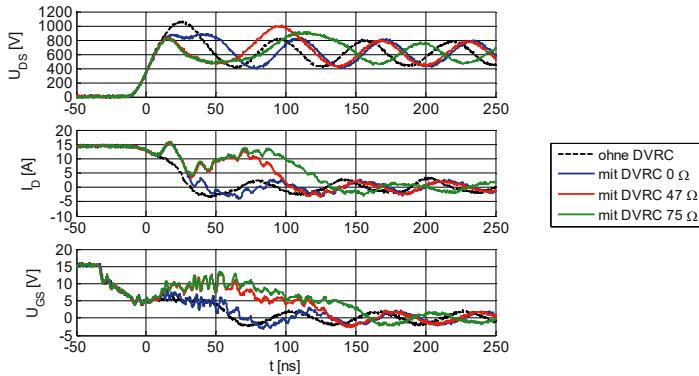

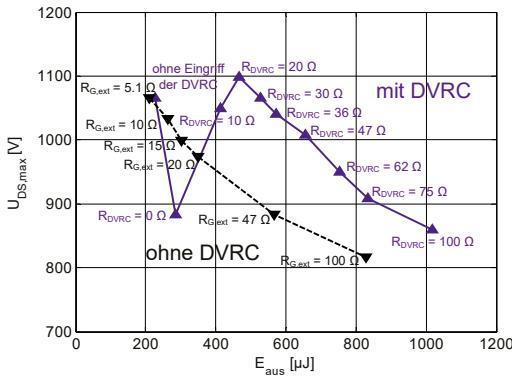

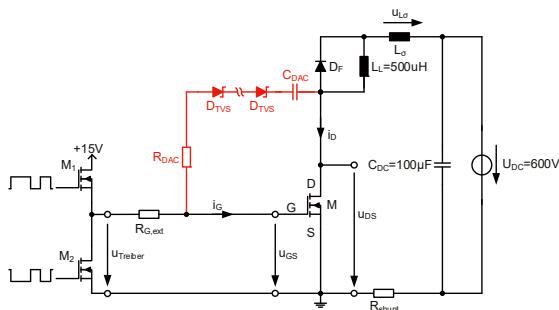

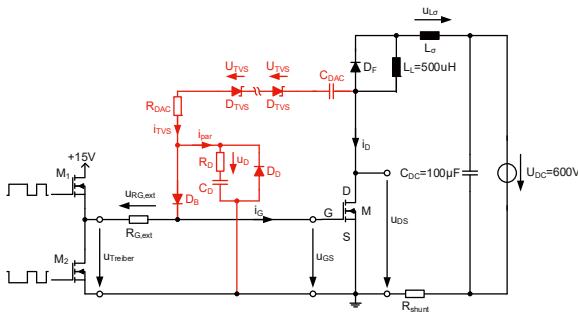

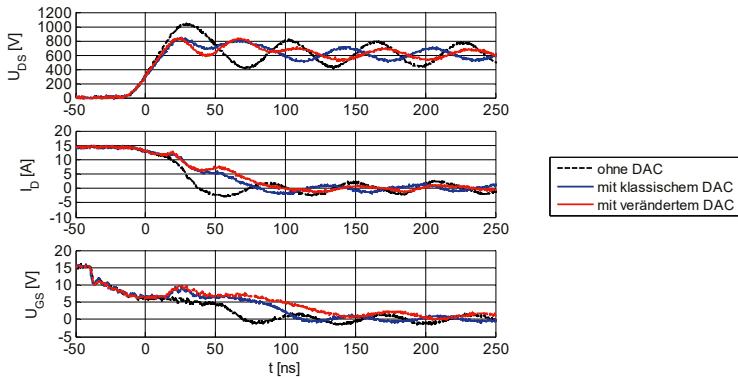

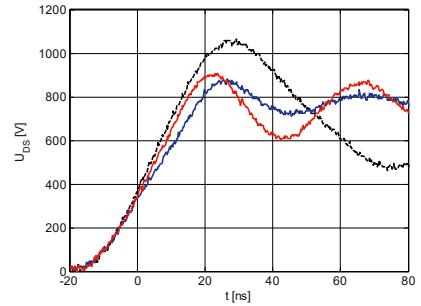

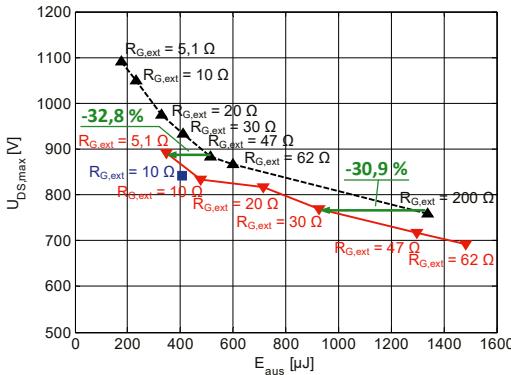

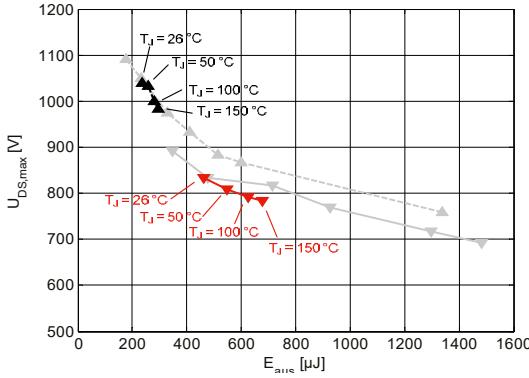

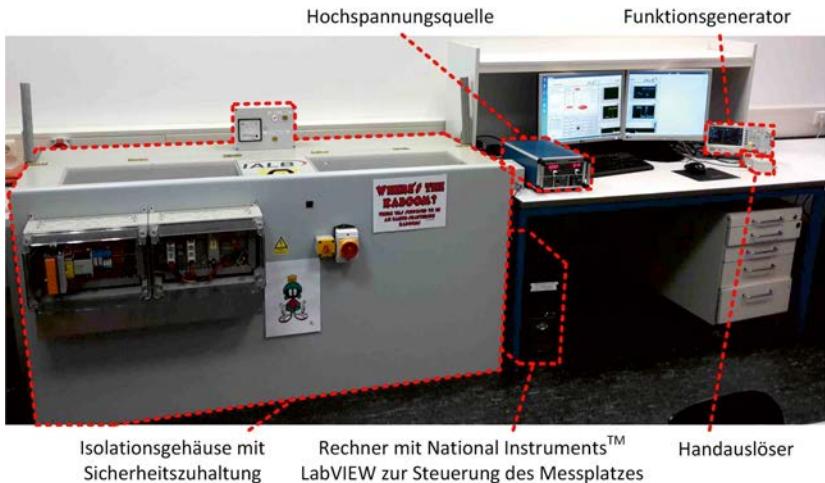

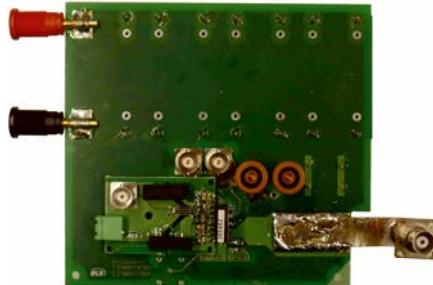

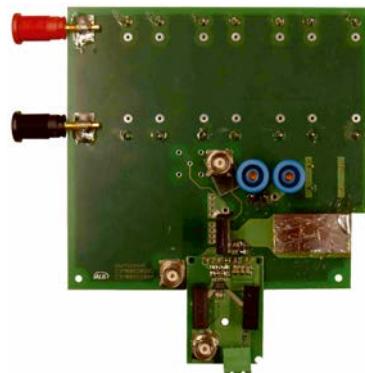

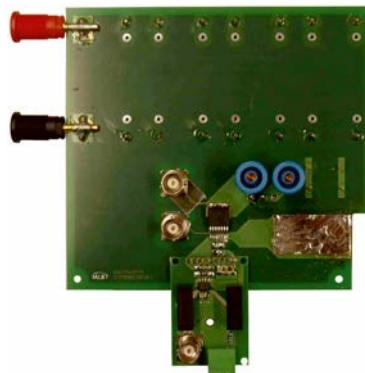

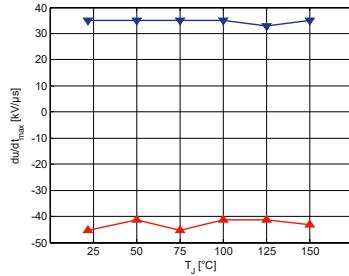

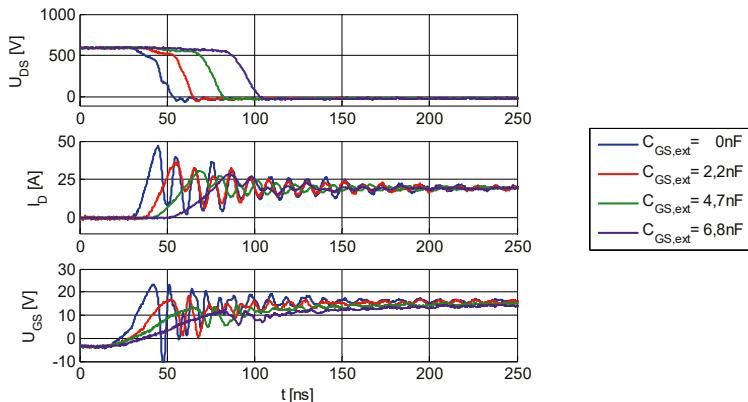

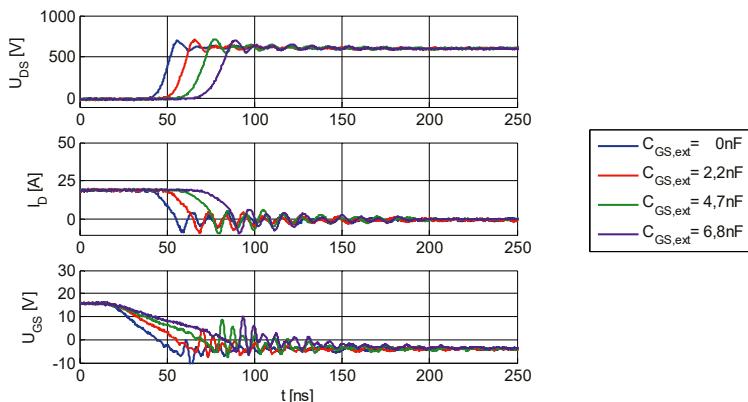

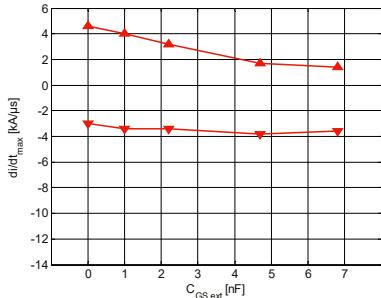

Nachteilig wirken sich beim Trench-MOSFET allerdings die hohen lokalen Belastungen an den Kanten des Gate-Oxids durch die elektrische Feldstärke E aus [HeDP16] [KNMN16]. Die Fragilität des Gate-Oxids gegenüber Belastungen durch die hohe elektrische Feldstärke E in SiC [HeDP16] [PSAB17] bildet beim SiC-MOSFET generell, neben der deutlich geringeren Beweglichkeit  $\mu_n^*$  im Kanal im Vergleich zur Beweglichkeit  $\mu_n$  im Volumenmaterial [KICo14] [PSAB17], eine der Schwachstellen.