# Fortschritt-Berichte VDI

VDI

Reihe 10

Informatik/

Kommunikation

Nr. 848

Herwig Unger, Wolfgang A. Halang (Eds.)

## Autonomous Systems 2016

Proceedings of the

9<sup>th</sup> GI Conference

FernUniversität in Hagen

Schriften zur Informations-

und Kommunikationstechnik

# Fortschritt-Berichte VDI

Reihe 10

Informatik/

Kommunikation

Herwig Unger, Wolfgang A. Halang (Eds.)

Nr. 848

Autonomous Systems

2016

Proceedings of the

9<sup>th</sup> GI Conference

FernUniversität in Hagen

Schriften zur Informations-

und Kommunikationstechnik

Unger, Herwig; Halang, Wolfgang A. (Eds.)

## Autonomous Systems 2016

### Proceedings of the 9th GI Conference

Fortschr.-Ber. VDI Reihe 10 Nr. 848. Düsseldorf: VDI Verlag 2016.

236 Seiten, 53 Bilder, 33 Tabellen.

ISBN 978-3-18-384810-2, ISSN 0178-9627,

€ 81,00/VDI-Mitgliederpreis € 72,90.

**Keywords:** Autonomous Systems – Safety-related and Real-time Systems – Networks and Routing – Suppression of Disturbances – Neural and Evolutionary Computing – Natural Language Processing – Education

To meet the expectations raised by the terms Industrie 4.0, Industrial Internet and Internet of Things, real innovations are necessary, which can be brought about by information processing systems working autonomously. Owing to their growing complexity and their embedding in complex environments, their design becomes increasingly critical. Thus, the topics addressed in this book span from verification and validation of safety-related control software and suitable hardware designed for verifiability to be deployed in embedded systems over approaches to suppress electromagnetic interferences to strategies for network routing based on centrality measures and continuous re-authentication in peer-to-peer networks. Methods of neural and evolutionary computing are employed to aid diagnosing retinopathy of prematurity, to invert matrices and to solve non-deterministic polynomial-time hard problems. In natural language processing, interface problems between humans and machines are solved with graph-based text representation and word segmentation. Finally, related aspects of teaching are discussed.

### Bibliographische Information der Deutschen Bibliothek

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliographie; detaillierte bibliographische Daten sind im Internet unter <http://dnb.ddb.de> abrufbar.

### Bibliographic information published by the Deutsche Bibliothek

(German National Library)

The Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliographie (German National Bibliography); detailed bibliographic data is available via Internet at <http://dnb.ddb.de>.

### Schriften zur Informations- und Kommunikationstechnik

Herausgeber:

Wolfgang A. Halang, Lehrstuhl für Informationstechnik

Herwig Unger, Lehrstuhl für Kommunikationsnetze

FernUniversität in Hagen

© VDI Verlag GmbH · Düsseldorf 2016

Alle Rechte, auch das des auszugsweisen Nachdruckes, der auszugsweisen oder vollständigen Wiedergabe (Fotokopie, Mikrokopie), der Speicherung in Datenverarbeitungsanlagen, im Internet und das der Übersetzung, vorbehalten.

Als Manuskript gedruckt. Printed in Germany.

ISSN 0178-9627

ISBN 978-3-18-384810-2

## Preface

Currently, the terms Industrie 4.0, Industrial Internet and Internet of Things, the latter one coined by Ashton in 1999 with regard to radio-frequency identification, are frequently heard buzzwords. According to the “New Gartner Hype Cycle for Emergent Technologies”<sup>1</sup> published in 2015, the topic Internet of Things has presently reached its “Peak of Inflated Expectations”, which is usually followed by the “Trough of Disillusionment”. Such a set-back is often caused by incorporating conventional items into new fashions<sup>2</sup>, that becomes visible when euphoria gives way to sober thinking. For a trend to prevail, it must then lead into the “Slope of Enlightenment”. To this end, real innovations are necessary, which can, with respect to the Internet of Things, to a large extent be brought about by information processing systems working autonomously on devices and network nodes of any kind as considered in this volume.

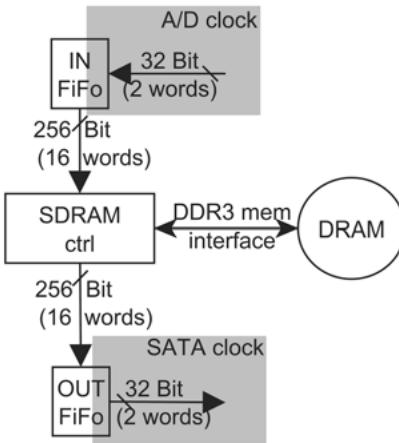

To begin with, in its first section on safety-related and real-time systems, well-established techniques for modeling safety requirements are reviewed and compared against essential requirements as provided by the standards prevailing for developing safety-related systems, a set of requirements for computer architectures to be inherently safe is derived from these standards, and verification and validation of robotic control software are discussed. For use in embedded safety-critical systems, a control unit is presented, whose main design criterion was verifiability by widest possible consensus, finally, a concept for an affordable, lossless storage of large amounts of measurement data generated on distributed mobile sensor nodes is worked out.

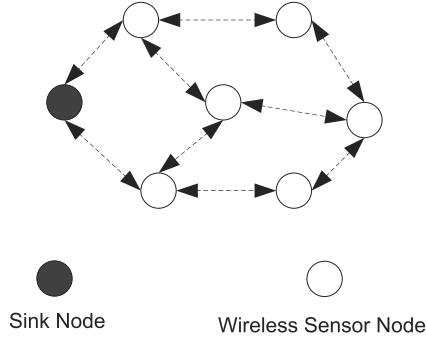

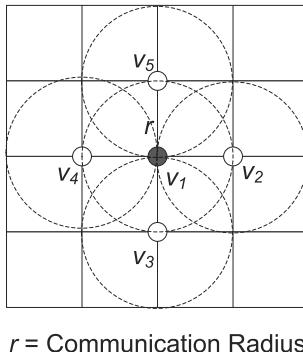

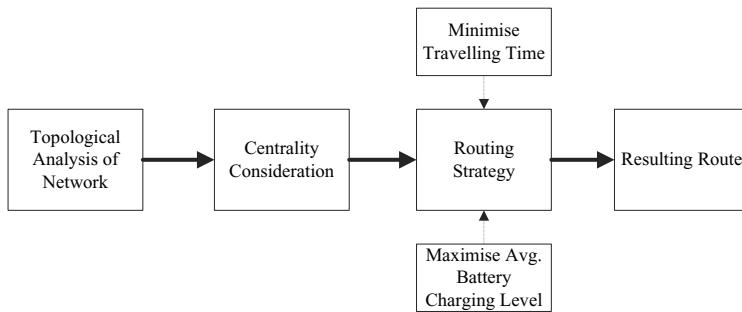

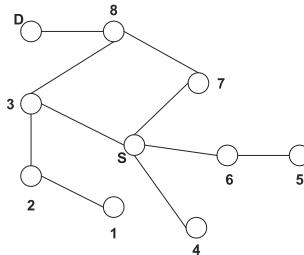

The section on networks and routing first deals with the use of centrality measures. Applying them and status data of sensor nodes, such as battery charging levels, a novel multi-criteria routing strategy for wireless sensor networks is proposed. In combination with topological analysis and information local in a network, then a routing algorithm aiming to maximise traffic flow and feasibility of selected routes is based on a new centrality measure. To ensure continuous re-authentication of peers in peer-to-peer networks, which were in contact before, finally a mechanism inspired by the dinner cryptographic protocol and the zero knowledge protocol is presented.

<sup>1</sup><http://www.gartner.com/newsroom/id/3114217>

<sup>2</sup>P. Mertens and D. Barbian: Digitalisierung und Industrie 4.0 – Trend mit modischer Überhöhung? *Informatik Spektrum* 39, 4, 301–309, 2016

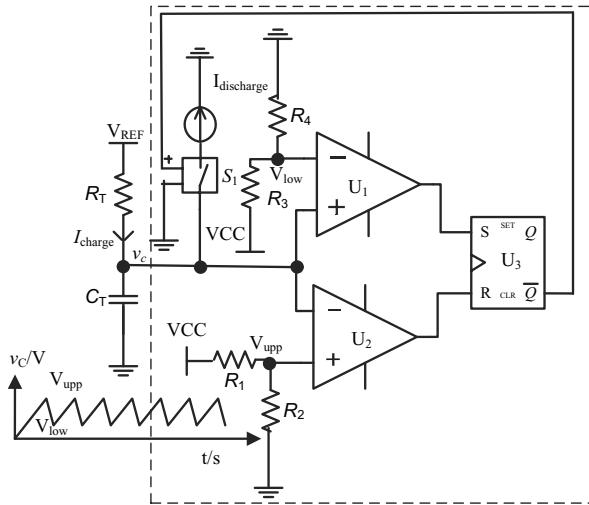

The following section is devoted to two approaches of suppressing disturbances. To this end, the feasibility of applying chaotic carrier frequency modulation for fighting electromagnetic interferences in switching-mode power supplies by spreading the spectra of input and output signals over the entire frequency band is shown, and the structure of a dual-mode passive filter is investigated by bifurcation analysis, which operates in dependence on a control parameter either as a band-pass or a high-pass.

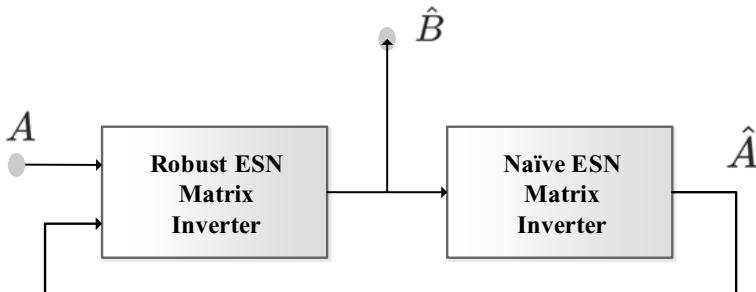

The first contribution in the section on neural and evolutionary computing details a method combining processing retinal images and machine learning with artificial neural networks in order to aid diagnosing retinopathy of prematurity, the most common cause of blindness of premature infants. Employing an echo state network as universal processing element, the concept of a novel matrix inversion system based on black-box-trained reservoir neurocomputing is then presented. Finally, according to the concepts of evolutionary computation and swarm intelligence, an improved quick artificial bee colony algorithm is proposed to solve a non-deterministic polynomial-time hard problem.

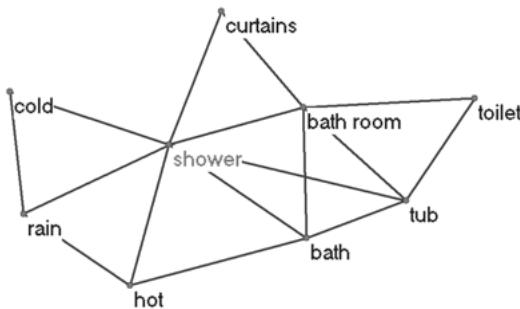

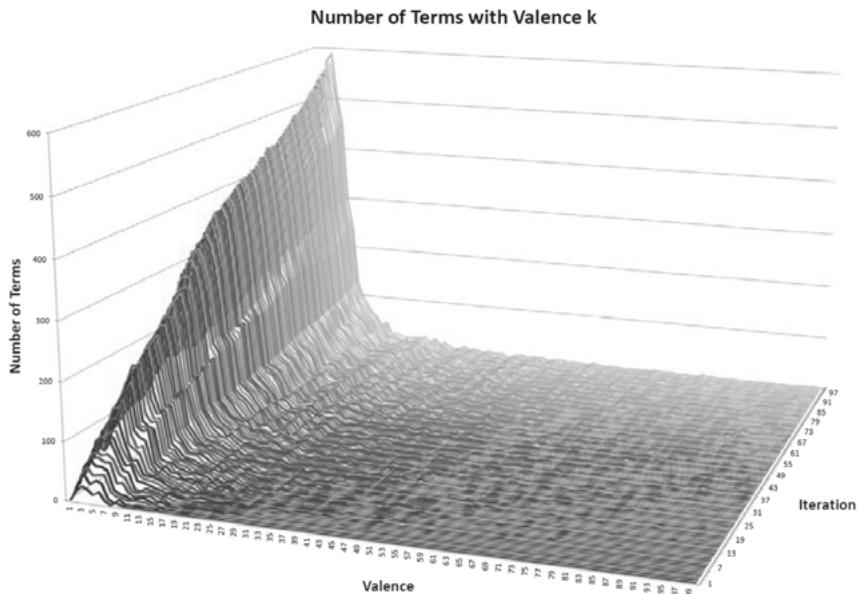

In the section on natural language processing a new graph-based method determining centroid terms as text representatives is presented, which allows to calculate semantic similarities between text documents — even if they have no terms in common, and the difficult task of word segmentation in the Thai language is shown to be improved by an algorithm employing automatically reorganising ranking tries and word usage frequency.

The section on teaching presents the unconventional view that interactive-style teaching as usually employed at universities of applied sciences is equivalent — if not even superior — to many modern approaches of teaching, and introduces an autonomous system for online exercises, which allows students to enter their solutions at any time, and which provides automatically generated feedback with a high degree of detail.

With teaching, here a hub facilitating ubiquitous online learning, also deals the first one of the conference presentations, of which only abstracts are provided in this volume. The further ones present a distributed event-triggered control algorithm to achieve consensus in heterogeneous multi-agent systems' outputs, applications of chaos theory for encryption, managing complex networks and suppression of electromagnetical interferences as exemplified for power converters by aperiodic pulse width modulation techniques, a novel approach of combining responses of selected Gabor filters shifted by certain off-set vectors, which

are automatically trainable for purposes of pattern recognition, and a method to estimate the values of graph parameters.

We are deeply indebted to Jutta Düring for her effort and care in achieving a consistent and appealing layout for this book, to Barbara Kleine for the administrative preparation of the conference, and to FernUniversität in Hagen for supporting the publication of this volume.

Herwig Unger

Wolfgang A. Halang

## Contents

### Safety-related and Real-time Systems

|                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| A Comparative Survey of System Specification Techniques for Safety-related Environments<br>D. Koß . . . . .                                               | 1  |

| Requirements for Safe Computer Architectures<br>S. Widmann . . . . .                                                                                      | 23 |

| Systematic and Probabilistic Testing of Autonomous Mobile Robots<br>F. Saglietti . . . . .                                                                | 40 |

| On the Construction of a Crowd-verifiable Microprocessor<br>M. Schaible . . . . .                                                                         | 46 |

| Affordable High-bandwidth Real-time Mass-storage Architecture for Distributed Sensor Nodes<br>M. Kirchhoff, C. Wagner, R. Herrmann and R. Thomä . . . . . | 55 |

### Networks and Routing

|                                                                                                                                     |    |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| Applying Centrality Measures in a Multi-criteria Routing Strategy for Wireless Sensor Networks<br>S. Sodsee and M. Komkha . . . . . | 70 |

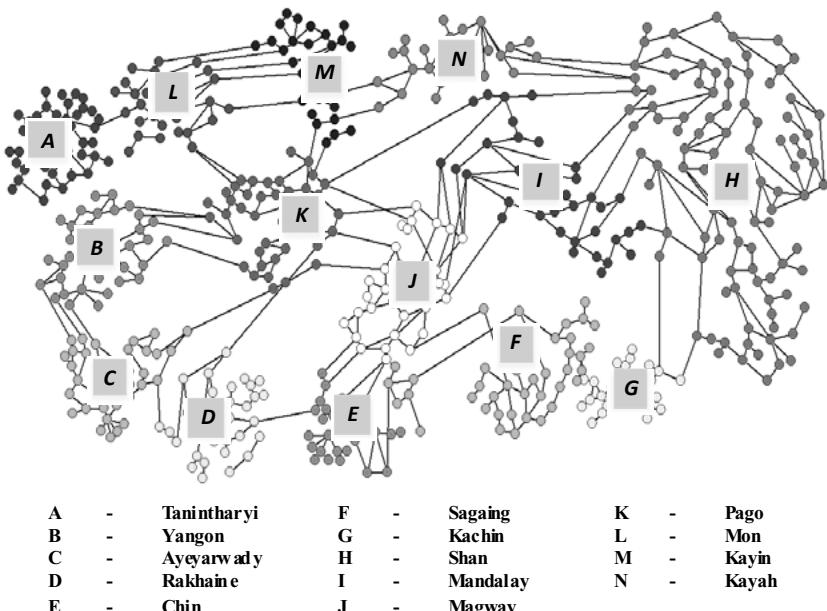

| Routing-based Topological Analysis on the Road Network in Myanmar<br>T. T. Naing and S. Sodsee . . . . .                            | 79 |

| Toward Authentication between familiar Peers in P2P Networking Systems<br>F. Nassermostofi . . . . .                                | 88 |

**Suppression of Disturbances**

Feasibility Study of Applying Chaotic Carrier Frequency Modulation in Switching-mode Power Supply

J. Niu, Y. Song, Z. Li and W. Halang . . . . . 104

Identification of Filter Types by Bifurcation Analysis: Mathematical Modelling and Numerical Simulation

N. Alain, H. B. Bieto, J. Ch. Chedjou and K. Kyamakya . . . . . 117

**Neural and Evolutionary Computing**

Retinopathy of Prematurity Classification based on Image Analysis

M. Sodanil and P. Thongrit . . . . . 133

Dual Echo State Networks-based Generalized Matrix Inversion with Applications in Stochastic Time-varying Systems

A. Haj Mosa, K. Kyamakya, M. Ali, H. B. Bieto and J. Ch. Chedjou . . . . . 144

Cardinality-constrained Portfolio Optimization using an improved quick Artificial Bee Colony Algorithm

D. Suthiwong and M. Sodanil . . . . . 156

**Natural Language Processing**

Centroid Terms and their Use in Natural Language Processing

M. M. Kubek and H. Unger . . . . . 167

Thai Language Segmentation by Automatic Ranking Trie

C. Tapsai, P. Meesad and C. Haruechaiyasak . . . . . 186

**Education**

Didactics in Computer Science Education at Universities of Applied Sciences

T. Tempelmeier . . . . . 195

Towards Live Feedback in Online Exercise Systems

H. Coltza and M. Badalus . . . . . 210

**Short Contributions**

|                                                                                             |     |

|---------------------------------------------------------------------------------------------|-----|

| Ubiquitous Communication Channels and E-Learning<br>D. Tavangarian, I. Waßmann . . . . .    | 219 |

| Coordinate-based and Service-centred Addressing for Routing in MANETs<br>A. Dilo . . . . .  | 221 |

| On Event-triggered Control with Application to Multi-agent Systems<br>G. Feng . . . . .     | 222 |

| All about Chaos<br>Z. Li . . . . .                                                          | 223 |

| Aperiodic Pulse Width Modulation in Power Converters for EMI Suppression<br>H. Li . . . . . | 224 |

| Trainable COSFIRE Filters for Pattern Recognition<br>N. Petkov . . . . .                    | 225 |

| Counting Efficiently Large Subgraphs Approximately<br>H. Lefmann . . . . .                  | 226 |

| <i>Index of Authors</i> . . . . .                                                           | 227 |

---

# A Comparative Survey of System Specification Techniques for Safety-related Environments

Daniel Koß

FernUniversität in Hagen, Germany

*Abstract:* Strong specifications are fundamental for systems development in safety-related environments. These specifications can be established by a systematic and sustainable requirements engineering. There are several well-established techniques of modelling requirements, of which an overview will be presented. Starting by describing less formal textual methods of requirements modelling, more and more formal methods are introduced. Finally, the specification techniques shall be compared against essential requirements that are given by standards for developing safety-related environments.

## 1 Introduction

### 1.1 The Sense of Specifying

Specifications serve to describe the overall structure and the operational behaviour of a system consisting of hardware and software components. Out of these specifications the system shall be able to be constructed (in the form of a development work) as well as be able to be understood (for maintenance or further development purposes).

Specifications, as a general rule, are more abstract than a system itself. If they were complete, they would contain the system itself. Therefore, specifications can also present a partial, defined view to the system. Specifications only contain the necessary information for a special case of use. A software part of a specification, for example, will probably contain little information about the hardware of the system, except the necessary requirements to run the software. Instead, the hardware specification will probably contain little information about the software part, except the necessary requirements to run the software on it. A system specification, however, will have its focus on the functional behaviour and the presentation of the system to the inner and outer peripherals, which

means the components that exist outside the system borders as well as the inner interfaces for software components. The inner details of the functionality of the hardware and software will be reduced to a necessary minimum to understand the overall functionality of the system.

Hardware and software as parts of an embedded system are dependent from each other, because without the one part the other part would hardly work, or, directly spoken, the one part makes no sense without the other part. Considering the software part separated from the hardware part, it could be hard to determine requirements from one part to the other timely and with the adequate attention. Within development phase of the software, for example, it may turn out, that the initially planned memory is not sufficient for the timely execution of the software. Here, a new requirement to the hardware is generated which claims to adjust the memory size.

Therefore, techniques and methods are necessarily needed to depict singular requirements to one part of the software or hardware component as well as relations and dependencies between the components. Especially in safety related environments, there is a strong need to model temporal conditions of the system's behaviour, for example the response time of a system, within which a functional correct answer has to be given. Furthermore, the behaviour of a system in the case of a failure must be specifiable. Within this paper an overview shall be presented of the state of the art of specification techniques as well as an analysis, if the techniques are suitable for specifying safety related requirements.

To achieve this goal, first requirements to specification techniques will be identified out of the standard IEC 61508. After that, well-established specification techniques will be investigated of their conformity against IEC 61508. Finally, a conclusion will be drawn, in what way these specification techniques are suitable to specify systems with safety related constraints.

## 2 Requirements for Specification Techniques according IEC 61508

The international standard IEC 61508 (entitled by "Functional Safety of Electrical/Electronic/Programmable Electronic Safety-related Systems") formulates requirements and instructions for the development of safety related systems with electrical, electronic and/or programmable components.

The parts 2 ("Requirements for electrical/electronic/programmable electronic safety-related systems") and 3 ("Software requirements") describe, among re-

quirements on management, documentation, design and validation/verification, requirements on requirement specification techniques. In [1] and [2] the following essential requirements on specification techniques and methods can be found ([1, tables B.1, B.2] as well as [2, table A.1]):

- Structure [A1],

- Visitability/verifiability [A2],

- Use of (semi-) formal methods (see [2, table B.7]) [A3],

- Traceability [A4],

- Computer-based [A5],

- Modularization of components [A6].

These slightly "soft" formulated properties shall on the one hand ensure as much freedom as possible on the selection of specification techniques for individual project needs, on the other hand unambiguously stipulate which fundamental procedures have been well-established and are therefore necessary for specifying safety related systems.

The IEC 61508 even becomes more concrete when describing what a specification has to afford. The following properties have to be expressible by a specification technique (compare [1, p.17] and [2, p.22]):

- Requirements to hardware and software components [B1],

- Internal and external interfaces [B2],

- Throughput and real-time characteristics, that means, time constraints [B3],

- Accuracy and robustness of subcomponents [B4],

- Failure behaviour, faulty behaviour and start-up behaviour [B5],

- Composition and architecture of subcomponents [B6].

With these properties the overall structure of a specification aswell as the least mappable content is set.

Furthermore, according to the standard, the following aspects have to be considered to support the design, development and later comprehensibility of a system consisting of hardware and software components:

- Support of a development life-cycle (compare [1], p.12 as well as [2], p.16) [C1],

- Clarity, precision, unambiguity, verifiability, testability, maintainability, executability (compare [1], p.17) [C2].

The requirements, that have been withdrawn from the standard, have been divided into requirements categories. The requirements marked by [Ax] are considered as necessary requirements, which presence is explicitly called. Requirements marked by [Bx] are less explicitly called, because there may be a strong dependence to the concrete project. Possibly, the one or the other requirement can be left out if there is no need to apply. But this proceeding, that is what the standard says, needs to be reasoned. Last but not least, the requirements marked by [Cx] serve as supportive methods, because their availability is hard to impose and hard to measure. These methods ultimately aim on a guideline for a defined structure and not for a defined matter.

### 3 Specification and Modelling Methods

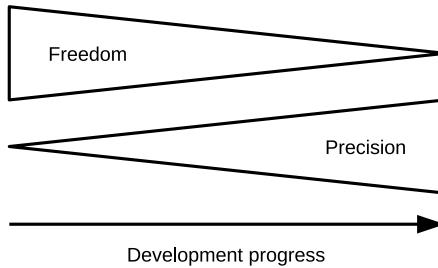

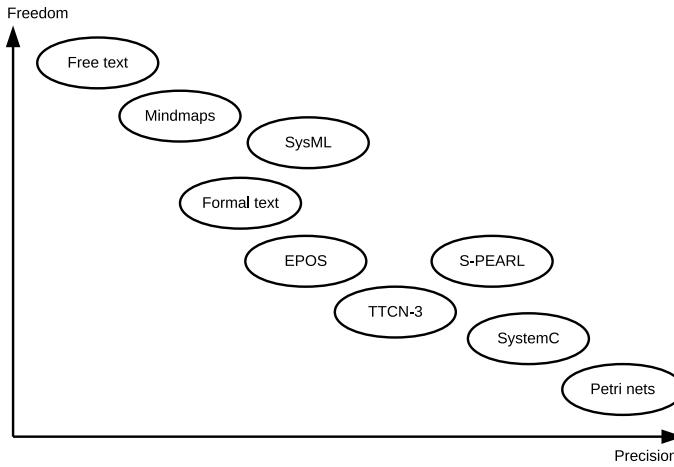

There can be a rough differentiation made between unstructured, structured and formal specification techniques. This classification is reasoned on a contrast of freedom on the one hand (which means, to model requirements as you want to in the actual context) and precision on the other hand (which means, to model requirements so that they are unambiguous).

Freedom and precision cannot be completely fulfilled simultaneously, therefore, depending on which development phase you are aiming or which case you are looking at, one has to decide, whether freedom or precision is more important. Naturally, the grade of freedom is continuously decreasing during ongoing development, because there have decisions to be made which reduce the remaining freedom. Simultaneously, the grade of precision increases continuously because of decisions that have been made and details that have to be established (see Figure 1).

Specifications firstly serve for supporting communication among people. Different instances of people have to formulate their thoughts and deliver them to other people, so that they are able to work with them or continue working on them. Because the receiving instance may belong to another company or even to another culture, it is necessary to communicate free of misunderstandings and standardized. Secondly, specifications serve for the construction of systems. This means, that the generated documents are the foundation for the

**Fig. 1:** Levels of detail of freedom and precision in increasing development progress

understanding and the implementation of the target system. For the implementation, specifications should have an adequate grade of detail, so that there is no possibility for interpretation. Therefore, we face the following conflicting objectives:

- Comprehensibility versus formalism.

- Clarity versus completeness.

- Communicability versus automatism.

These conflicting objectives are mainly a detailed list of the conflict of freedom versus precision, which has been shown in Figure 1. For specification techniques the conflicting objectives mean, that both of them could not simultaneously be fulfilled in the same quality. There are only two possibilities to resolve the conflicts:

- Using different specification techniques depending on the case of use,

- Using specification techniques, that are able to scale the level of detail depending on the case of use.

The surveyed specification techniques shall be analysed to what extent they are suitably usable within safety-related real-time data processing.

### 3.1 Unstructured Specification Techniques

The main characteristics of unstructured specification techniques are, that there are no formal, structural or methodical restrictions for writing them. Therefore, a relatively large degree of freedom is given which implies initial creativity and supports finding ideas. A disadvantage of this freedom is, that understanding a specification made this way requires a large amount of interpretation. This

interpretation space can have a wide spread for project members that have different backgrounds, either organizational or even cultural. Eventually, the receiving user of the specification misses essential information, that would have been forced to give by the writing within a given structure. Therefore, an unstructured specification technique, like the ones presented as follows, can only be established with an external definition of a proceeding regulation.

### Free Text

The probably most natural method to specify requirements is to write them down the way they come in mind, for example as a free text. An example for a customer requirement in a free text manner:

"I wish that the system would not freeze that often."

A requirement, formulated in such an informal way, misses the following characteristics:

- Bindingness: it is not possible to determine, of which urgency this requirement is.

- Unambiguousness: there is a definition missing, what is meant by "freeze that often", that is, a quantification is missing.

- Precision: there is a definition missing, what the abstract term "freeze" exactly means and how this behaviour can be measured.

In a free text of a system specification, like the example above, it first must be identified what the real requirements to the system are and how it will later be possible to validate them. Therefore, a free text can only be the first step to collect and describe basic ideas and write down and structure first concepts.

It is not reasonably possible to use a free text as a specification document for suppliers or corresponding developers. For a requirement formulated like this, a transformation must be done into a format that allows a structured processing first.

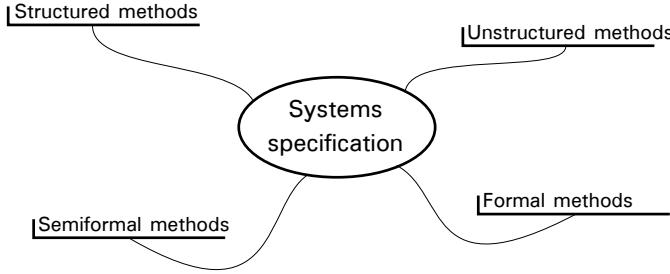

## Informal Visualization

The most familiar informal visualization technique is mind mapping. Mind maps allow structuring ideas and thoughts roughly and make it possible to connect them with lines and arrows to visualize relations among each other. See Figure 2 for a simple example of a mind map.

**Fig. 2:** Simple example of a mind map for structuring ideas

The advantage of having the freedom to paint roughly and quickly what is going through one's mind is also the biggest disadvantage of this method. Though mind maps and other informal visual specification techniques allow to bring a first structure into a specific topic, these methods are missing a structural proceeding. Therefore, their applicability for safety-related systems is normally not suitable. Every mind map can have a different structural appearance and there is much interpretative effort needed to extract relevant information out of a mind map. Normally, there is additional information needed to interpret the mind maps significance and meaning, for a example by a template.

## 3.2 Structured Specification Techniques

### Formal Text

More purposeful than describing requirements in a free text manner is by undergoing the text to a formalism. This can be achieved, for example, with a text template wherein the composition of a requirement's structure is specified so that it contains all relevant information for the design as well as for the verification of the system. An example for a customer requirement in a formal text manner:

"The system shall answer correctly on a signal income within 100 milliseconds."

This requirement fulfils the following formalism:

1. Who has to do something?

2. What has to be done?

3. How binding is the requirement?

In the example at hand the questions can be answered as follows:

1. The system has to do something.

2. Answering correctly after a certain time from a signal income.

3. It has to be fulfilled under all circumstances.

The system behaviour can be validated clearly and under several circumstances against the requirement, for example under average load or high load. The result is then a binary statement, with which it is possible to say the system passed or failed under the specified constraints.

An extension to the principle of text templates is the principle of document templates. With document templates the whole structure of a specification document is given. This affects the layout of the chapters as well as the proceeding of the document creation, for example by requirements elicitation, review techniques and release processes. A document created by this process is easier to understand, because not only the content, but also the way of creating the document is standardized. Furthermore, with document templates it is easier to communicate across organizational borders. Every participating organisation just needs to know the template to follow the structure of the document and is easily able to analyse the content. Further information is given in the standard ISO/IEC/IEEE 29148 (see [3]), which standardizes life cycles of system specification documents.

## EPOS

The computer based system EPOS (Engineering and Project management Oriented Support system) serves for the holistic view on project planning of software development and supports every development phase of a software development process [4, p.67]. Thereof:

- Requirements elicitation,

- Project management,

- System design,

- Quality management.

To support the single project steps, EPOS is divided into different mark-up languages and supporting tools which are:

- EPOS-R: language for requirements elicitation,

- EPOS-S: language for system design specification,

- EPOS-A: analysis tool,

- EPOS-D: documentation tool,

- EPOS-P: project management language and

- EPOS-M: general management tool.

A requirement in EPOS-R looks like as follows:

REQUIREMENT 0815 (0):

<SafeState>

"Within safe state, the system

has to turn off all of its outputs."

An event on the systems layer, described in EPOS-S, looks like as follows:

EVENT CriticalFailure

DESCRIPTION:

PURPOSE: "When a critical failure occurs,

get into safe state."

DESCRIPTIONEND.

INTERRUPT FROM RegularExecution

EVENTEND

A project resource can be described with EPOS-P in the following way:

TEAMMEMBER Meyer-M.

CATEGORY: 'Test', 'Project'

FUNCTION: "Testmanager"

RESPONSIBILITIES: Testing

ASSIGNMENTS:

Testing 80%,

## Requirements 20%

### TEAMMEMBEREND

An advantage of this method is, that every project-related requirements and constraints can be integrated and linked together and then be accessed in a single system without changing the environment. Because every project member uses the EPOS tools with his or her own access rights it is guaranteed, that every member works on the same, consistent database. Additionally, requirements can be traced from design over implementation to test case. That simplifies project work tremendously.

It cannot be denied that a disadvantage of EPOS is the maintenance of the system. Working with EPOS means that every project member needs to spend additional effort continuously throughout the project lifetime and this has to be done with discipline and sustainability. Because once the database contains inconsistent data, every project member works with this inconsistent data, what provokes unforeseeable consequences for the project.

## Specification Languages

### TTCN-3

Another structured specification technique is the specification of requirements by test cases. This method is also known as "test driven development" and is aiming at the circumstance, that the correct implementation of a system is only verifiable by testing. If the test cases are given at the beginning of development, it is possible to develop in such a way to pass the test cases. At the same time the developer has the proof, that he or she worked correctly if the test cases passed.

For the test driven development one can use the text-based technique TTCN-3 (Testing and Test Control Notation version 3) which is a language specifically designed for the specification of test cases and test scenarios [6]. TTCN-3 syntactically follows well-known programming languages like C/C++ and Java.

As an example, a test case for a server application shall be developed which initially sends a Ping request to a server and awaits an Echo answer from the server within a defined time interval (follows [6, Listings 1-6]). The test description is structured as follows. First, the module description has to be defined, which defines interfaces and data types for the test case:

```

module pingTest{

type record urlType {

charstring protocol,

charstring host

}

template urlType urlTemplate := {

protocol := "ping",

host := "www.fernuni-hagen.de"

}

...

}

```

Next, the component description takes places, in which the expected answer from the server is described:

```

...

type component ptcType {

port httpPortType httpPort;

timer localTimer := 3.0;

}

type port httpPortType message {

out urlType;

in echo;

}

type component mtcType {}

type component systemType {

port httpPortType httpPortMsg;

}

...

```

At last, the implementation of the test case itself is implemented, in which the modules and components are initialized and executed (with PTC = parallel test component, MTC = main test component):

```

...

testcase DoPing1 ( )

runs on mtcType system systemType {

var ptcType ptcTester;

ptcTester := ptcType.create;

map(ptcTester : httpPort, system : httpPortMsg);

ptcTester.start(ptcBehaviour()));

```

```

all component.done;

}

...

```

Additionally, sub functions, that are needed and called by the test case, are specified as follows:

```

...

function ptcBehaviour() runs on ptcType {

httpPort.send(urlTemplate);

localTimer.start;

alt {

[] httpPort.receive(echo) {

localTimer.stop;

setverdict(pass);

}

[] httpPort.receive {

localTimer.stop;

setverdict(fail);

}

[] localTimer.timeout {

setverdict(fail);

}

}

}

```

Finally, on top hierarchical layer, the functionality itself is executed by a control call. The test case in the example above is passed, if the Echo response is received within 3 seconds after the Ping request. Else, the test fails.

Furthermore, the programmed test scenarios can be viewed as graphical representations. There is no transformation of the textual description needed, because both representations are equivalent. The graphical representation can be used for communication purposes with other project members, for example with less technical versed ones.

Advantageous of working with TTCN-3 is the strict formalism of this specification technique as well as the proof, that the system has been developed correctly, when the test cases pass. Disadvantageous is, that TTCN-3 is only of limited usability for communicating between project members, because more or less expert knowledge is needed to understand the specified test environment.

Furthermore, dependencies between different states of the targeted system are hard to model, because there is a test case needed and needs to be maintained for every state and every state transition of the system.

Depending on the targeted project it can be an advantage or a disadvantage that test cases are specified only on top systems layer. There is no demand given if a test case requires implementation in software or hardware. This potentially can have disadvantages for the later reuse of single subcomponents.

It can be stated positively that a system specification with this technique explicitly allows to give time constraints and time-outs. This is an advantage for specifying real-time systems, because at any time the given time constraints are known and can be tested thoroughly.

## SystemC

SystemC is a system modelling and description language which is an extension of the programming language C++ with components for hardware description. SystemC is especially useful to specify the following constructs on systems layer:

- Parallelism,

- Synchronism,

- Interprocess communication.

SystemC has special qualities in verifying and simulating specifications that have been designed in this language, because SystemC constructs are compilable and executable. Thereby, it is possible to verify components on a relatively high abstraction layer, with which statements of performance and robustness are possible early in development. A disadvantage of SystemC is that for interpreting a system description as a specification, deeper knowledge in C++ as well as additional knowledge in SystemC is mandatory. This means, that SystemC is less reasonable for requirements elicitation, but is more reasonable to design the system itself.

Beneath, a simple rising edge triggered flip flop is described as an exemplification how digital logic can be described in SystemC (from [5, p.12]):

```

// dff_pos_edge.h

#include "systemc.h"

```

```

SC_MODULE(dff_pos_edge){

sc_in<bool> clk;

sc_in<bool> din;

sc_out<bool> dout;

void doit();

SC_CTOR(dff_pos_edge){

SC_METHOD(doit);

sensitive_pos << clk;

}

};

// dff_pos_edge.cpp

#include "systemc.h"

#include "dff_pos_edge.h"

void dff_pos_edge :: doit(){

dout = din;

}

```

## S-PEARL

S-PEARL (Specification Process and Experiment Automation Language) is a concept, which is an extension of the programming language PEARL and which uses a similar syntax and structure. PEARL is especially suitable to specify concurrency and time constraints in relation to real-time conditions, which is not intuitively supported by other programming languages. PEARL was especially designed for real-time data processing and supports time constraints within its fundamental functionality. S-PEARL picks up the concept of modularity and the overall structure of PEARL and can be used to specify hardware and software parts simultaneously (see [9]).

A processing unit, which processes an input sensor signal and emits an actor control signal, can be described as below (follows [9, p.13]):

ARCHITECTURE:

```

STATIONS;

NAMES: STAT;

PROCTYPE: MSP430 AT 20 MHz;

...

INTERFACE: MSP_IO

```

```

(DRIVER: MSP_INOUT; DIRECTION: INOUT);

STATIONTYPE: NORMAL;

TICK: 1E-6 SEC;

SYSTEM;

NAMES: STAT;

STAT.MSP_IO INPUT;

NAMES: SENSOR;

SENSOR.OUT OUTPUT;

NAMES: ACTUATOR;

ACTUATOR.IN INPUT;

SYSEND;

CONFIGURATION:

COLLECTION MSP_PER;

PORTS MSP_1, MSP_2;

CONNECT MSP_PER.MSP_1

IN SENSOR.OUT VIA STAT.MPS_IO;

CONNECT MSP_PER.MSP_2

OUT ACTUATOR.IN VIA STAT.MPS_IO;

COLEND;

MODULES MSP_Mod1;

EXPORTS(T1);

TASK T1

TRIGGER PORT MSP_1;

...

OUTPUT PORT MSP_2;

TASKEND;

MODEND;

CONFEND;

ARCHEND;

NET;

STAT.MSP_IO <-> SENSOR.OUT;

STAT.MSP_IO <-> ACTUATOR.IN;

NETEND;

```

### 3.3 Semi Formal Modelling Methods

#### Systems Modelling Language

The Systems Modelling Language (SysML) is a modelling language designed for modelling systems, that consist of hardware and software components. It has arisen from the Universal Modelling Language (UML) which is a generic, graphical specification and design technique that has mainly been designed for software systems design [8, p.8]. Its diagrams can be subdivided into two categories with seven diagram types, respectively:

1. Structure diagrams,

2. Behaviour diagrams.

The following diagram types have been borrowed for SysML out of UML:

- Structure diagrams:

- Use case diagram (allows modelling a system, its actors and system borders),

- Sequence diagram (allows modelling a sequence of events),

- State diagram (allows modelling states and transitions between the states),

- Activity diagram (allows modelling elementary actions and their interconnections),

- Behaviour diagrams:

- Package diagram (allows modelling logical groupings and their dependency relations),

- Internal block diagram (allows modelling architectures and parts of it, for example subsystems),

- Block definition diagram (allows modelling blocks and their internal interconnections as well as block interfaces).

The most important SysML specific diagram types are the following:

- Requirement diagram (behaviour diagram type, allows modelling system requirements).

- Parametric diagram (structure diagram type, allows modelling constraints and assurances to a continuously working (physical) system).

The diagram types exist hierarchically in parallel than hierarchically vertical. That means, that there is no specification which diagram type has to be used in a certain development phase. Different diagrams just allow different views onto the same system. Use case diagrams, for example, describe the system and its borders to the surrounding environment and its actors, respectively. State diagrams are mainly used to describe the internal behaviour of a system. Furthermore, diagrams are scalable nearly endlessly. Parts of a diagram can, for example, refer to more detailed sub diagrams, whereby the complexity of a diagram is significantly manageable. For a certain demand it is possible to dive into special sub diagrams that give a view onto certain partial functionality without losing the overall context. At the same time, a developer will not be overburdened by too much information that is not necessary for his or her actual work.

Because UML and SysML, respectively, were not primarily designed for the use within safety-relevant real-time environments, trade-offs or modifications have to be made. It is the nature of these modelling languages that they can be customized by profiles domain specifically, so that they are tailored for the required design purpose.

An example for a profile that allows modelling real-time constraints is the MARTE profile (Modelling and Analysis of Real-Time Embedded Systems) [7] which extends UML. With this profile there is a special aspect of real-time modelling highlighted, that is, time. It especially allows defining time periods and time limits, respectively, within which a system has to provide a functional correct answer. MARTE distinguishes between the following flavours of time: [7, p.57]:

- Asynchronous, in the form of a temporal order (causal),

- Synchronous, in relation to a time basis (discrete) and

- Physical, that means expressing time periods by units.

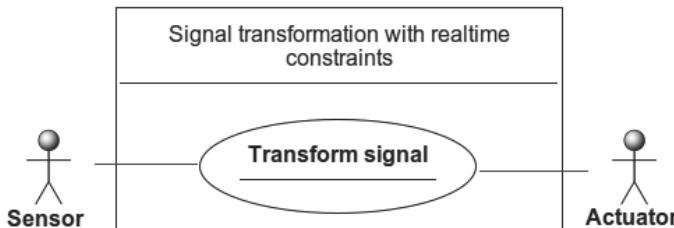

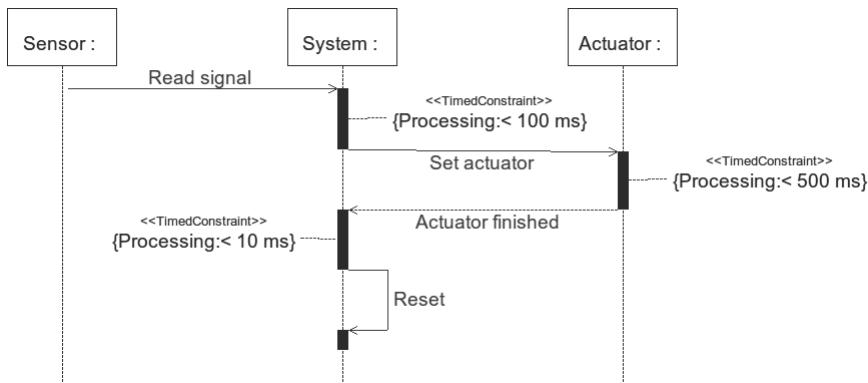

As a practical example, a system consisting of a hardware and a software component shall be modelled. Therefore, the following requirements are elicited:

- A sensor input shall be read,

- An actor output shall be set,

- The sensor signal shall be transformed in a certain way,

- After the input signal comes up, the output of the actor signal shall be finished within a defined time limit.

The following diagrams will be created:

- use case diagram, for separating the system from its environment and defining the actors (Figure 3),

- sequence diagram, for modelling the chronological sequence of the activities (Figure 4).

Fig. 3: Use case diagram with system boundaries

Fig. 4: Sequence diagram of communication interaction with timed constraints

### 3.4 Formal Modelling Methods

Formal modelling methods mean to be correct by proof. That means, that one is able to examine the correctness of a system against its formal specification. If the examination is successful, the proof of correctness is adduced. The nature of formal methods is their formalism, that means strict notation and absolute precision. This makes them unambiguous, but maybe hard to understand and less flexible. One example for such a formal method is the concept of petri nets, with which concurrent systems can be described formally. The most important characteristics are (compare [4, p.351]):

- Clarity,

- Modelling of dynamic behaviour,

- Abstraction,

- Verifiability,

- Computer-based.

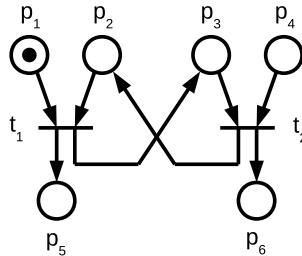

A (marked) petri net is defined by  $PM = (P, T, Pre, Post, m_0)$  with

- $P$ : a finite set of places (states),

- $T$ : a finite set of transitions,

- $P \cap T = \emptyset$ , that means, that places cannot be transitions and vice versa,

- $Pre$ : an input arc function with  $P \times T \rightarrow \mathbb{N}$ ,

- $Post$ : an output arc function with  $T \times P \rightarrow \mathbb{N}$ ,

- $m_0$ : initial marking.

As an example, a flip flop element shall be modelled as a petri net. The flip flop shall be a 4-tuple of the form  $(P, T, Pre, Post)$ . Then the following shall apply:

$$P = \{p_1, p_2, p_3, p_4, p_5, p_6\}$$

$$T = \{t_1, t_2\}, \text{ mit } P \cap T = \emptyset$$

$$Pre(p_1, t_1) = Pre(p_2, t_1) = Pre(p_3, t_2) = Pre(p_4, t_2) = 1$$

$$Post(t_1, p_5) = Post(t_1, p_3) = Post(t_2, p_2) = Post(t_2, p_6) = 1$$

Where  $Pre(p_n, t_m)$  is an arc from place  $P$  to transition  $T$  and  $Post(t_m, p_n)$  is an arc from transition  $T$  to place  $P$ . All input and output arcs that are equal to zero

have been omitted because of clarity. A visualization of this petri net is given in Figure 5. It is obvious, that the presentation of petri nets in formulas can

**Fig. 5:** A flip flop logical circuit modelled by a graphical petri net with initial marking of the set input

be confusing, if complex behaviour with several external influences has to be modelled. At the same time, error potential increases if petri nets are not modelled computer-based or with automatic validation methods. The advantage of graphical representations of petri nets is, that complex interactions and relations can be perceived quickly and dynamic behaviour can be presented clearly.

## 4 Comparison

Finally, the presented specification and modelling techniques shall be compared against to the requirements A1 - A6 out of chapter 2.

| Method      | Structural | Verifiable | Semiformal | Traceable | Computerized | Modular |

|-------------|------------|------------|------------|-----------|--------------|---------|

| Free text   | -          | -          | -          | -         | -            | o       |

| Mindmaps    | o          | -          | o          | -         | +            | +       |

| Formal text | +          | o          | -          | -         | o            | o       |

| EPOS        | +          | o          | o          | +         | +            | o       |

| TTCN-3      | +          | +          | +          | o         | +            | +       |

| SystemC     | +          | +          | o          | +         | +            | +       |

| S-PEARL     | +          | +          | o          | +         | +            | +       |

| SysML       | +          | o          | +          | -         | +            | +       |

| Petri nets  | +          | +          | o          | -         | o            | o       |

Furthermore, a classification of its level of detail is given in Figure 6 in comparison to Figure 1. In this diagram one can see which specification techniques might be more useful at a specific step in the process of system development, though it is not forbidden to use a technique out of the order when it makes sense. The use of a specification technique strongly depends on the specific project needs.

**Fig. 6:** Qualitative classification of the techniques' level of detail

## 5 Conclusion

Unstructured, non-traceable techniques for the specification of safety-related embedded systems have become obsolete. The use of structural methods, that allow a traceability through the whole development life cycle, is state of the art.

A huge gain of value is provided by specification methods, that allow an implementation directly out of the specification, like SystemC or S-PEARL do. With this proceeding the effort that needs to be spent, in contrast to using different specification techniques, is less. Unfortunately these methods are hard to understand for personnel without deeper technical background. Therefore, these

methods, at their actual function volume, can at the earliest be used in detailed specification phase, and not likely in the requirements elicitation at the beginning. Here, UML and formal text methods show benefits at early concept phase, where SystemC, TTCN-3 and S-PEARL have advantages at late specification phase until early implementation phase.

Future investigations could go into the direction of an automatized tool chain that supports handling requirements from the elicitation over implementation until testing and releasing, where human interference is driven down to an unavoidable minimum.

## References

- [1] International Electrotechnical Commission: IEC 61508-2 - Part 2: Requirements for electrical/electronic/programmable electronic safety-related systems. 2010

- [2] International Electrotechnical Commission: IEC 61508-3 - Part 3: Software requirements. 2010

- [3] International Standardization Organization et al.: ISO/IEC/IEEE 29148 - Systems and software engineering – Life cycle processes – Requirements engineering. 2011

- [4] Halang, W.A., Li, Z.: Prozessautomatisierung/Echtzeitsysteme II. FernUniversität in Hagen, 2009

- [5] Muhr, H.: Einsatz von SystemC im Hardware/Software-Codesign. Diplomarbeit an der Technischen Universität Wien, Fakultät für Elektrotechnik, 2000

- [6] Schieferdecker, I. et al.: The Test Technology TTCN-3. In: Hierons, R.M. et al. (Eds.): Formal Methods and Testing, Lecture Notes in Computer Science. Springer Berlin Heidelberg, 2008

- [7] Object Management Group: UML Profile for MARTE: Modeling and Analysis of Real-Time Embedded Systems Version 1.1. OMG document number: formal/2011-06-02. <http://www.omg.org/spec/MARTE/1.1>

- [8] Korff, A.: Modellierung von eingebetteten Systemen mit UML und SysML. Spektrum Akademischer Verlag. Heidelberg, 2008

- [9] Gumzej, R.: Engineering Safe and Secure Cyber-Physical Systems. Springer International Publishing. Switzerland, 2016

---

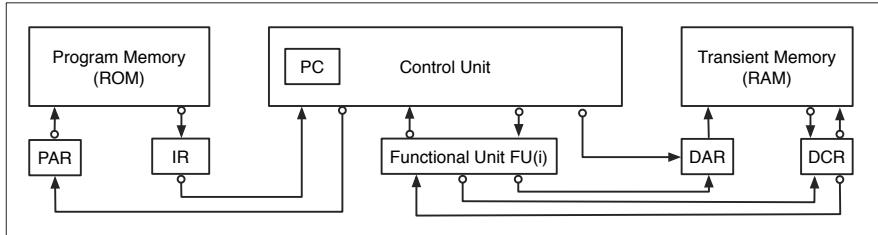

# Requirements for Safe Computer Architectures

Stefan Widmann

Chair of Computer Engineering, FernUniversität in Hagen, Germany

*Abstract:* Embedded systems are used in rising numbers of safety-related applications, e.g. steer-by-wire and brake-by-wire in automotive applications. At the same time, complexity of hard- and software of such systems is increasing and the reduction of the minimum feature sizes of used integrated circuits makes them more sensitive to environmental influences, resulting in a rising number of software and hardware errors. Instead of trying to detect those errors by even more complex software, 23 requirements for safe computer architecture hardware are presented that have been derived from the standard IEC 61508 parts 2 and 3 and various typical software errors. The most commonly used conventional architectures x86 and ARM are evaluated based on these requirements.

## 1 Introduction

Safety-related applications that have been realized using pure mechanical or electromechanical systems before are more and more realized by programmable systems today. Good examples are automotive and avionic applications like braking, steering and flying: brake-by-wire, steer-by-wire and fly-by-wire replace the proven and reliable mechanical systems by electrical and electronic sensors and actors, the sensors' signals being processed by microprocessors to calculate control signals for the actors [26–28].

At the same time the complexity of software used in embedded systems is rising. In 2006, Broy states in [29], that a car contains about 10 million lines of code and that he expects a rise by the factor ten with each car generation. Three years later, in 2009, Broy is cited in [31], stating that the number of lines of code has risen to 100 million. In 2008, a future rise to 200 to 300 millions was estimated in [30].

Complexity of hardware is rising, too. Over 70 embedded systems were used in a car in 2006 [29] and up to 100 in 2009 [31]. On chip level, the number transistors

per die has reached 1.3 billion in 2015 [34]. The integration of growing numbers of components in integrated circuits is only possible due to a continuous reduction of the minimum feature size, making them more sensitive to environmental influences like radiation, especially neutrons, even on ground level [32, 33].

All of this results in rising numbers of software and hardware errors. Since commercial-off-the-shelf (COTS) microprocessors commonly used in such systems are not designed to provide effective means for error prevention and detection on hardware level, more and more complex software is used to detect errors during runtime, e.g. by applying arithmetic coding in the form of Software Encoded Processing (SEP) and Compiler Encoded Processing (CEP) [25]. This additional software complexity results in additional software errors.

Instead of continuing to focus on error detection on a software level, 23 requirements for the hardware of a safe computer architecture have been derived from the international standard for safety-related system, the IEC 61508, and various descriptions of frequent and dangerous software errors. By applying these requirements to the hardware of a computer system, they enforce error prevention and detection on a superior level.

The most commonly used conventional computer architectures – x86 and ARM [21] – are evaluated regarding their conformance to these requirements.

## 2 Requirements for safe computer architectures

Hardware is designed, implemented and tested once, while software goes through its complete lifecycle in every new project. By applying requirements for software to the underlying hardware, software conformance to the requirements can be enforced on hardware level and a superior overall error prevention and detection can be achieved.

### 2.1 Requirements derived from IEC 61508

The most important source regarding requirements for the design of safety-related systems is the international standard IEC 61508, consisting of seven parts, -1 to -7. Part 2 describes the requirements for the hardware design of safety-related systems, part 3 does the same for software design and part 7 contains extensive details for both parts. All of the requirements listed below are derived from the IEC 61508 parts 2, 3 and 7 [5–7].

### **Detection, reporting and handling of errors**

For the domains software, hardware, sensors and actors there shall be means to detect and handle errors. It is also necessary to report detected errors.

*R 1: A safe architecture shall provide features to detect, report and handle errors in software, hardware, sensors and actors.*

#### **Means to enter and stay in a safe state**

During design of software and hardware means shall be realized allowing the system to enter and stay in a safe state in case of errors, if such a safe state exists in the specific system.

*R 2: A safe architecture shall provide means to enter and stay in a safe state.*

#### **Means for error detection**

Redundant configurations and especially diverse redundancy shall be possible for error detection.

*R 3: A safe architecture shall be able to provide (diverse) redundant configurations.*

To detect errors in volatile and non-volatile memories, in registers and during transmission of data, error detecting Hamming or polynomial codes shall be used.

*R 4: A safe architecture shall apply integrity checks like Hamming or polynomial codes for error detection.*

If Hamming codes are used for error detection, it shall be realized as Extended-Hamming-Code, increasing the Minimum Hamming Distance to 4 by adding an additional parity bit.

*R 5: If using a Hamming Code for error detection, it shall be realized as Extended-Hamming-Code with a Minimum Hamming Distance of four.*

Even if the integrity checking means allow error correction, data that has been identified as corrupted shall not be corrected, since – depending on the number of erroneous bits – a correction attempt could result in a valid, yet wrong data word, without the possibility to detect this faulty correction on a higher level.

*R 6: A safe architecture shall not try to correct data identified as faulty, but reject it instead.*

## Error handling

A safe architecture shall provide means to handle occurring errors and shall allow graceful degradation, e.g. by using redundant units or running less time consuming data processing functions with less accuracy.

*R 7: A safe architecture shall provide means to handle occurring errors and shall allow graceful degradation.*

## Error prevention and good maintainability

The development of safety-related software requires error prevention by application of measures to keep complexity as low as possible. The proposed way to achieve this are modularity, encapsulation and information hiding, providing software maintainability with a low probability of introducing additional errors.

*R 8: A safe architecture shall support modularity of software at hardware level by providing means for encapsulation and information hiding.*

## Realization of time driven software architectures

A cyclic and absolutely deterministic behavior of software is required, with guaranteed response times. This shall be achieved by realization of time driven architectures with fixed execution time slots for the different software parts. This leads to the requirement for only supporting synchronous programming.

*R 9: A safe architecture shall support synchronous programming and time driven software architectures by hardware means and shall not support asynchronous programming.*

## Avoidance of dynamic objects

It is a frequent software error, not to free all dynamically allocated memory after being used (so called memory leaks), resulting in a rising memory consumption over runtime. Such errors are hard to find during testing. If a system runs out of memory, handling these type of error is very complicated in an embedded system.

*R 10: A safe architecture shall not support dynamic objects.*

## Strong typing

Strongly-typed programming languages are to be used to prevent data handling errors without any implicit type conversions. The same requirement can be applied to the underlying hardware:

*R 11: A safe architecture shall provide strong typing without implicit type conversions on a hardware level.*

When doing explicit type conversions, strict rules shall be applied.

*R 12: A safe architecture shall apply a strict set of rules for data type conversions.*

## Limitation of language features

If there are unsafe or hard-to-test language features, coding guidelines shall forbid the use of such features. A safe architecture can support this requirement by preventing the realization of problematic features.

*R 13: A safe architecture shall prevent the realization of unsafe language features and thus limit them to a safe and easy-to-test subset.*

## Structured programming

For improved error prevention and increased maintainability structured programming shall be used. Especially, this is important when using low-level languages like assemblers. A safe architecture shall enforce structured programming to support this requirement.

*R 14: A safe architecture shall enforce the use of structured programming.*

## Avoidance of pointers

Pointers are being provided by many programming languages for easy access of data. They are especially used when handling dynamic objects in memory. Common errors regarding pointers are usage of Null pointers, accessing data outside of arrays, structures and objects and accessing freed dynamic objects. These types of errors are hard to uncover during testing, hard to analyze and do often show up after long time.

*R 15: A safe architecture shall not support the use of pointers, but provide means to realize safe array handling, including detection of out-of-bounds accesses as errors.*

### Avoidance of recursions

Recursive programming produces hard-to-test programs, since correctness is hard to prove. This applies especially for the prove of convergence over the whole range of input values. An additional problem is the dependency of stack memory consumption on the input values.

*R 16: A safe architecture shall not support recursion, leading to a reduction of realizable language features (see R 13, too).*

### Application of special rules regarding floating point arithmetics

When using floating point data types, serious programming errors can be implemented regarding sequence of evaluation and checking equality of floating point values. While the sequence of evaluation can only be influenced on a software basis, a safe architecture shall not provide means to test for equality of floating point data types.

*R 17: A safe architecture shall not provide instructions to check equality of floating point data types.*

### Avoidance of interrupts

Interrupts weaken the determinism of temporal behavior of software. They can be avoided, if events are polled instead, making their handling absolutely deterministic.

*R 18: A safe architecture shall not support interrupts.*

## 2.2 Requirements derived from typical software errors

Further requirements are derived from typical software errors based on [3, 10–15] and directed towards the hardware of safe computer architectures.

### Usage of uninitialized variables

Usage of data without assigning a meaningful value first is a frequent programming error [13]. Based on the initialization of the runtime environment of the used programming language and maybe an operating system, this can result in the usage of wrong or random values.

*R 19: A safe architecture shall detect usage of uninitialized variables as error.*

### Out-of-bounds accesses in arrays

Out-of-bounds accesses – accessing data outside of an array, structure or object – are frequent programming errors [11, 14, 15], which can cause memory corruption, information disclosure vulnerabilities and wrong computation results. In [15], this type of error is on the 3rd place of the 25 most dangerous programming errors. Since arrays are vital to most programming languages and implementations, a safe architecture shall provide means for safe array handling, as already specified in R 15.

### Pointer related errors

As already mentioned before, pointers bare the risk of dangerous and hard to detect errors [13, 14]. This results in the already formulated requirement R 15.

### Errors regarding data type interpretation and type conversion

Errors regarding interpretation of variable's contents and type conversion errors have caused huge damage [10, 12, 14]. A corresponding requirement has already been formulated in R 11.

### Arithmetic under- and overflows

Under- and overflows can happen during arithmetic operations and are not always detected and handled properly [12, 15]. This type of error is on the 24th place of the 25 most dangerous programming errors in [15].

*R 20: A safe architecture shall provide means to realize safe arithmetics, being able to detect under- and overflows as errors.*

### Division by zero

A division by zero is undefined and results in raising an exception on most architectures [3, 12].

*R 21: A safe architecture shall detect divisions by zero as errors.*

### Missing checks of function parameters and return values

Many typical software vulnerabilities could be avoided if strict checks would be applied to input and output data [11]. This applies to a system's input and output data as well as on parameters passed to a function and its return values on the lowest level.

*R 22: A safe architecture shall provide means to check function parameters and return values.*

### 2.3 Requirement regarding avoidance of arithmetic registers

Nearly all conventional architectures provide a set of registers, some of them dedicated to special functions, others for general purpose. Tanenbaum and Goodman demand in [17], that powerful architectures shall have at least 32 general purpose registers. Management of those registers by compilers is called register allocation and is complex to realize [4, 18]. To determine the validity of the contents of registers, the variables those contents correspond to and how long they must stay valid, highly complex algorithms are used, called live variable analysis [18]. In [1] an architecture without arithmetic registers is introduced, resulting in less complex compilers and thus a less probability of compiler errors.

*R 23: A safe architecture shall not provide arithmetic registers.*

## 3 Conventional architectures x86 and ARM

The most commonly used conventional architectures are x86 and ARM [21]. While the x86 architecture is typically used in desktop PCs and industrial computers, ARM processors are predominantly used in mobile devices such as smartphones and tablets, due to their low power consumption.

### x86 architecture

Although first steps towards advanced protection features were implemented in the Intel 80286, the Intel 80386 was the first x86 processor that provided a fully featured safe operation mode called protected mode [3], which provides two different types of protection, segmentation and paging.

In segmentation data structures called descriptors are used, specifying a segment's base address, the segment's size and its properties. There are code and

data descriptors, identifying code and data segments as such. The contents of code segments are always non-writable and the contents of data segments are always non-executable. By selecting the appropriate properties in the descriptor of a segment, a code segment can be made non-readable and a data segment can be flagged as read-only. Any violation of these rules will be detected by the processor and a general protection fault is raised [3]. Another important property of a descriptor is the specification of its privilege level, expressing the least privilege needed to access the contents of a corresponding segment. The 80386 provides 4 privilege levels and they are often called rings. Code and data running in a ring 0 segment has or requires the highest privileges, code and data in ring 3 the least. In practice, only two of the four privilege levels are used, e.g. in the operating system Linux [19]: ring 0 is used by the operating system kernel and drivers and ring 3 is used by user code.

The paging mechanisms, hierarchically located below segmentation, provide two levels of privilege, supervisor and user, and specify, whether a page is read-only or read- and writable. There was no possibility to mark pages as non-executable until AMD introduced the NX bit in the page table entries in the Athlon 64 processor [24]. That means, prior to that extension, there was no way to prevent execution of data if segmentation was not used to the full extent.

Although segmentation provides strong safety features, in practice the two most commonly used operating system Microsoft Windows [8] and Linux [19] only use a flat memory model, which was proposed in [3]. In a flat memory model, code and data segments of a program are set to the same base addresses and the length of the segment is set to maximum, making it easy for the operating system to access a program's whole memory. This disables nearly all protection features offered by segmentation, leaving mainly only those provided by paging. Segmentation and its protection features aren't available in the modern 64 Bit mode of x86 processors [9], so the only available protection features are those of the paging functionality provided by the Memory Management Unit MMU.

## ARM architecture

The company behind the ARM architecture, ARM Ltd., does not produce processors itself. Instead it is granting licenses to other companies to integrate ARM processor designs into their own products [23]. Those designs are optimized towards low power consumption and are widely used in embedded devices such as smartphones and tablets [21].

An ARM processor offers up to nine different modes of operation, of which the three relevant modes are supervisor mode for operating systems, system mode for privileged applications and user mode for standard user applications [2, 20].

In contrast to the x86, ARM processors do not provide segmentation as a protection feature. All encapsulation is to be done using the paging mechanisms of the integrated Memory Management Unit MMU [20]. First implemented in ARMv6, the XN bit (eXecute Never), similar to the NX bit of the x86, allows the software to mark memory pages as non-executable to protect data from being interpreted as code. Not all ARM processor designs raise exceptions on a division by zero, some just return zero as the result [20]. The memory architecture can be – depending on the selected processor design – realized as von-Neumann or Harvard architecture [22].

## 4 Evaluation of x86 and ARM architectures

Based on their conformance to the 23 requirements for safe computer architectures, both conventional architectures x86 and ARM shall be evaluated. Each requirement is judged based on the level of conformance to the requirement each of the architectures is providing: full conformance, partial conformance and no conformance to a requirement.

### **R 1: A safe architecture shall provide features to detect, report and handle errors in software, hardware, sensors and actors**

x86 and ARM provide full conformance: Both conventional architectures provide means for error detection, signalization and handling, e.g. in the form of exceptions.

### **R 2: A safe architecture shall provide means to enter and stay in a safe state**

x86 and ARM provide partial conformance: Entering a safe state must be requested by the software itself in the corresponding exception handlers, since there is no dedicated supervisory hardware instance.

**R 3: A safe architecture shall be able to provide (diverse) redundant configurations**

**R 7: A safe architecture shall provide means to handle occurring errors and shall allow graceful degradation**

x86 and ARM provide full conformance: Redundant configurations are possible in x86 and ARM based systems, as well as graceful degradation, but such configurations must be handled by software.

**R 4: A safe architecture shall apply integrity checks like Hamming or polynomial codes for error detection**

**R 5: If using a Hamming Code for error detection, it shall be realized as Extended Hamming Code with a Minimum Hamming Distance of four**

**R 6: A safe architecture shall not try to correct data identified as faulty, but reject it instead**

x86 and ARM provide partial conformance: Some systems – especially servers – based on x86 and ARM provide error correcting codes ECC. This ECC is usually realized using an Extended-(72,64)-Hamming-Code [16], but it only covers the contents of the external memory and the connection to the memory controller. A comprehensive check of all data paths throughout the system including all of the processor's internal data paths and registers isn't provided. Detected errors are corrected if possible, which violates requirement R 6.

**R 8: A safe architecture shall support modularity of software at hardware level by providing means for encapsulation and information hiding**

x86 provides full conformance: The x86 provides isolation features in the Protected Mode based on segmentation and paging. Both mechanisms are complex and must be managed by software, e.g. the operating system. Using the segmentation in full extent is omitted in Windows and Linux [8, 19], and only the protection features of paging come into effect. The x86 cannot provide protection on a single data word level, but requirement R 8 must still be considered as fulfilled using segmentation and paging.

ARM provides full conformance, too: The ARM architecture does not provide segmentation, but provides isolation measures based on paging. It doesn't pro-

vide protection on data word level, but requirement R 8 must still be considered as fulfilled using paging.

**R 9: A safe architecture shall support synchronous programming and time driven software architectures by hardware means and shall not support asynchronous programming**

x86 and ARM provide no conformance: Both architectures provide means to support asynchronous programming, making them non-conforming to requirement R 9.

**R 10: A safe architecture shall not support dynamic objects**

x86 and ARM provide no conformance: The conventional architectures x86 and ARM do not limit the software in matters of memory handling, making it easy to implement and use dynamic objects.

**R 11: A safe architecture shall provide strong typing without implicit type conversions on a hardware level**

**R 12: A safe architecture shall apply a strict set of rules towards data type conversions**

X86 and ARM provide no conformance: Neither x86 nor ARM architectures provide means to identify data types of memory contents. The same applies to the differentiation of code and data. The interpretation of memory contents is based on how the software tries to access them, e.g. trying to execute them or apply specific instructions.

**R 13: A safe architecture shall prevent the realization of unsafe language features and thus limit them to a safe and easy-to-test subset**

**R 16: A safe architecture shall not support recursion, leading to a reduction of realizable language features**

x86 and ARM provide no conformance: Both architectures don't restrict the usable language features, and recursive function calls are not detected as errors.

**R 14: A safe architecture shall enforce the use of structured programming**

x86 and ARM provide no conformance: The conventional architectures x86 and ARM don't enforce usage of structured language features.

**R 15: A safe architecture shall not support the use of pointers, but provide means to realize safe array handling, including detection of out-of-bounds accesses as errors**

x86 and ARM provide no conformance: Pointers are supported in both architectures and explicitly supported by corresponding addressing modes. Checking of pointers and range checks when accessing arrays must be implemented in software.

**R 17: A safe architecture shall not provide instructions to check equality of floating point data types**

x86 and ARM provide no conformance: If a Floating Point Unit FPU exists, both architectures provide explicit instructions to check equality of floating point values.

**R 18: A safe architecture shall not support interrupts**

x86 and ARM provide no conformance: Interrupts are supported by both architectures. Applications that do not use interrupts but poll for occurred events instead can be realized, but the hardware does not enforce polling. thus the requirement cannot be considered as fulfilled.

**R 19: A safe architecture shall detect usage of uninitialized variables as error**

x86 and ARM provide no conformance: Data in memory cannot be flagged as uninitialized on x86 and ARM architectures. The protection features of paging can be used to raise exceptions on read accesses to uninitialized memory pages with coarse granularity, but there are no means to realize this on a single data word level. This requirement cannot be considered as fulfilled.

**R 20: A safe architecture shall provide means to realize safe arithmetics, being able to detect under- and overflows as errors**

x86 provides no conformance: The x86 architecture does not detect arithmetic under- or overflows as errors, software must explicitly check for them.

ARM provides partial conformance: Some ARM designs support saturating additions and subtractions. This leads to a partial conformance to requirement R 20.

### **R 21: A safe architecture shall detect divisions by zero as errors**

x86 provides full conformance: The x86 generates a division by zero exception in case software tries to divide by zero.

ARM provides only partial conformance: Not all ARM designs raise an exception on trying to divide by zero. Some return zero as the result [20], which cannot be distinguished from a correct result. Therefore this requirement can only be considered as partially fulfilled.

### **R 22: A safe architecture shall provide means to check function parameters and return values**

x86 and ARM provide no conformance: No checks are applied to function parameters and return values unless the checks are implemented in software.

### **R 23: A safe architecture shall not provide arithmetic registers**

x86 and ARM provide no conformance: Both architectures provide general purpose registers that can be used for arithmetic operations.

## **Evaluation results**

The results of the evaluation are shown in table 1, which shows the low conformance of both conventional architectures x86 and ARM. While the x86 architecture conforms to 5 requirements, the ARM architecture conforms to only 4 of them. There are 14 requirements the x86 and 13 the ARM architecture does not satisfy at all. In contrast, the Inherently Safe Microprocessor Architecture ISMA, which was introduced in [35], provides full conformance to 22 and partial conformance to 1 of the requirements.

## **References**

- [1] H. Stieger, W. A. Halang: Eine hochsprachenorientierte Rechnerarchitektur ohne arithmetische Register; 1st edition, 2003; IFB Verlag Paderborn; ISBN 3-931263-39-8

- [2] U. Brinkschulte, T. Ungerer: Mikrocontroller und Mikroprozessoren; 3rd edition, 2010; Springer Verlag; ISBN 978-3-642-05397

- [3] Intel: 80386 System Software Writer's Guide; 1991; ISBN 1-55512-023-7

- [4] R. Güting, M. Erwig: Übersetzerbau; 1999; Springer Verlag; ISBN 978-3-540-65389-9

**Table 1:** Evaluation and comparison of x86, ARM and ISMA

| Requirement | x86 | ARM | ISMA |

|-------------|-----|-----|------|

| R 1         | +   | +   | +    |

| R 2         | (+) | (+) | +    |

| R 3         | +   | +   | +    |

| R 4         | (+) | (+) | +    |

| R 5         | (+) | (+) | +    |

| R 6         | (+) | (+) | +    |

| R 7         | +   | +   | +    |

| R 8         | +   | +   | +    |

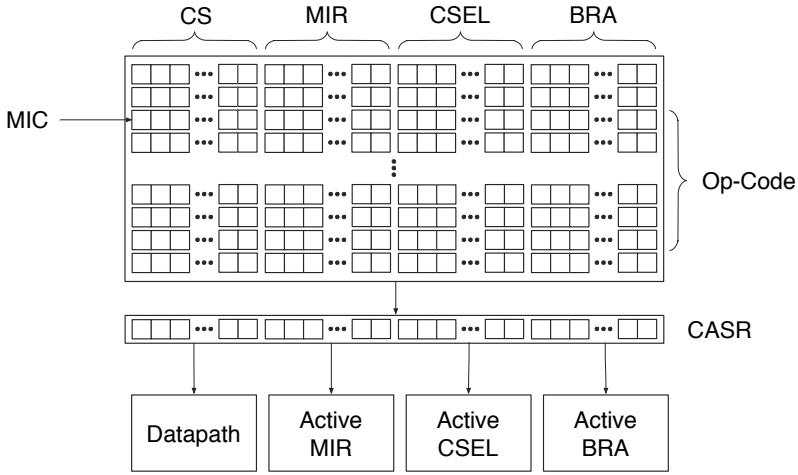

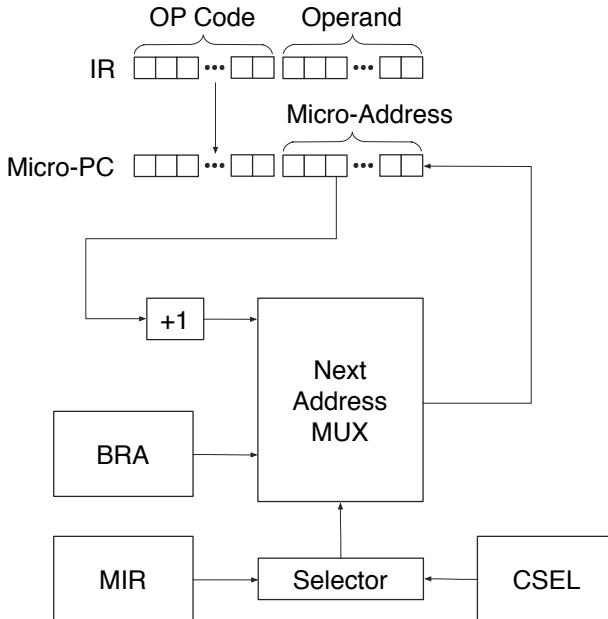

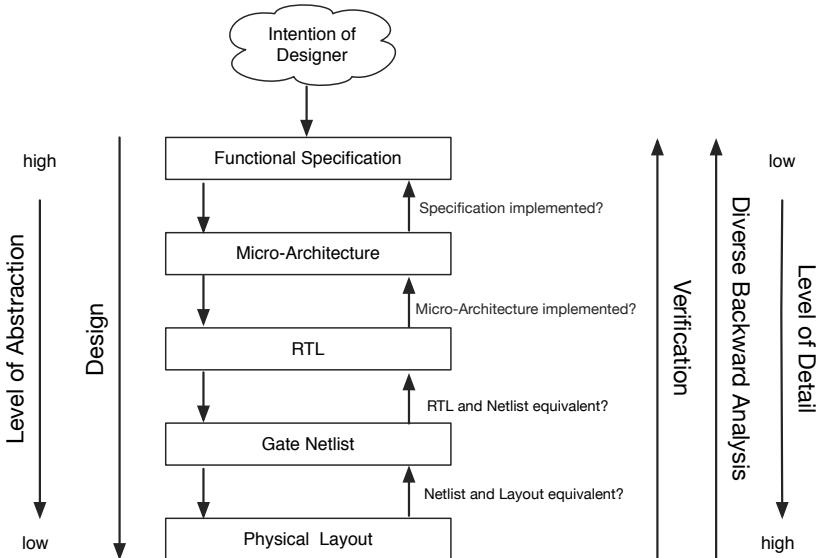

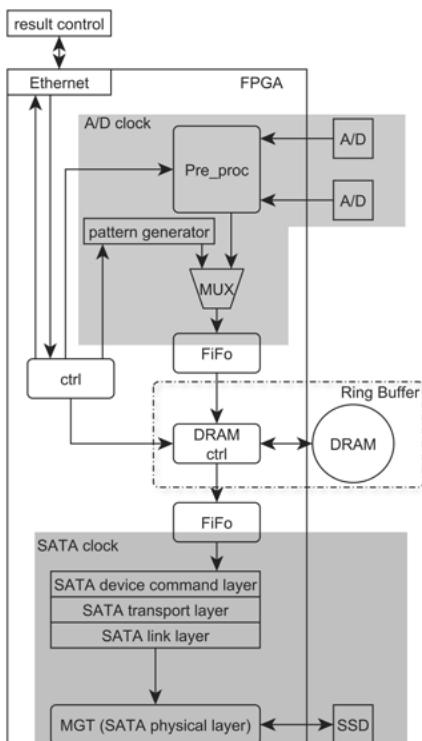

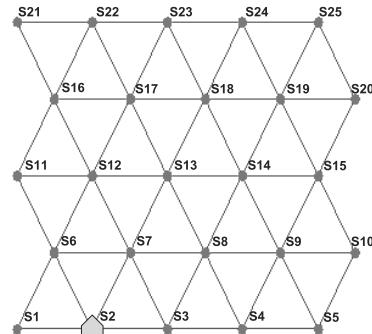

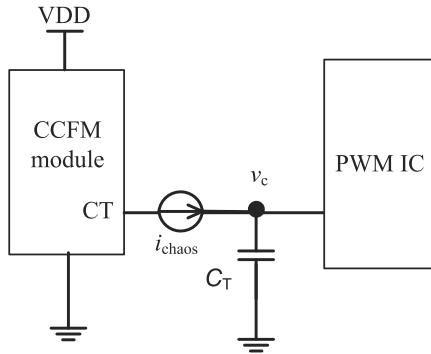

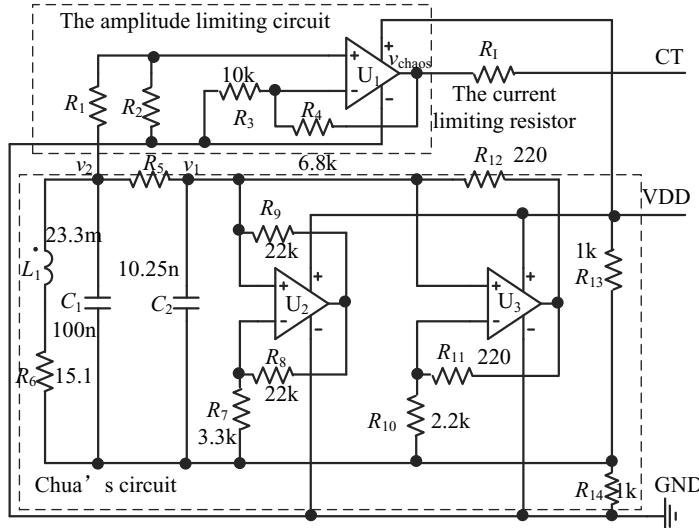

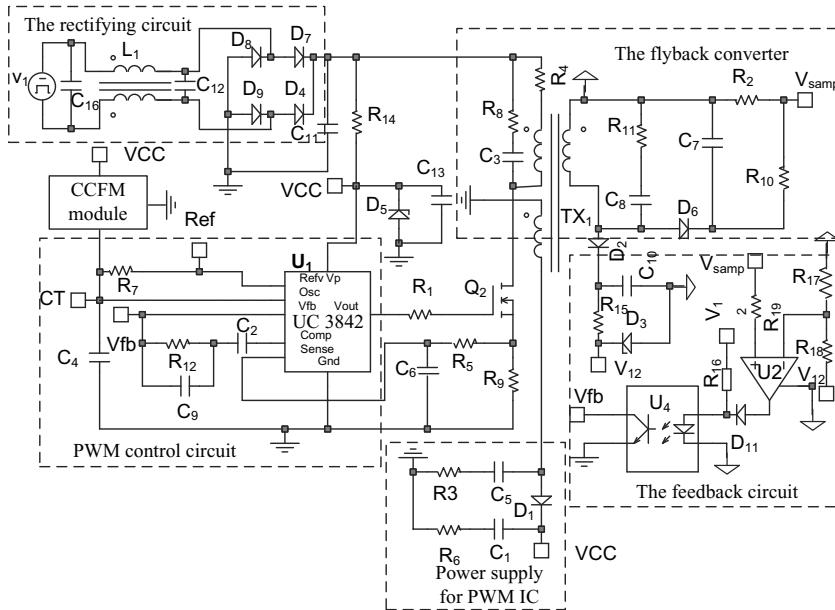

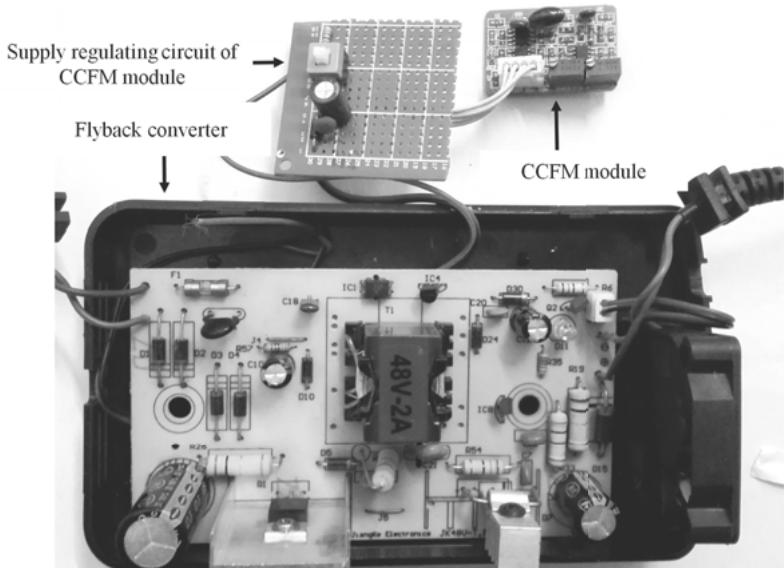

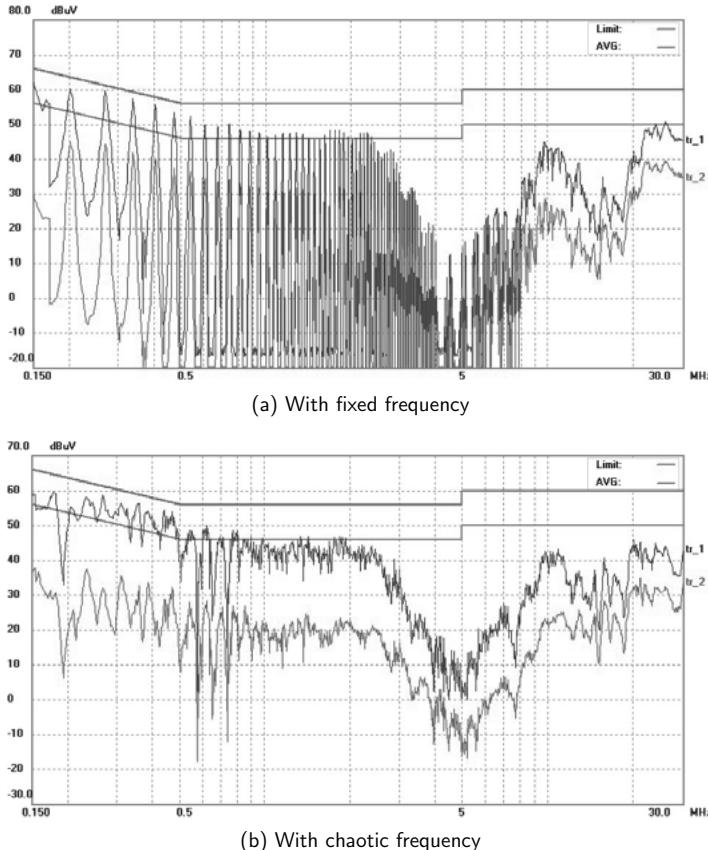

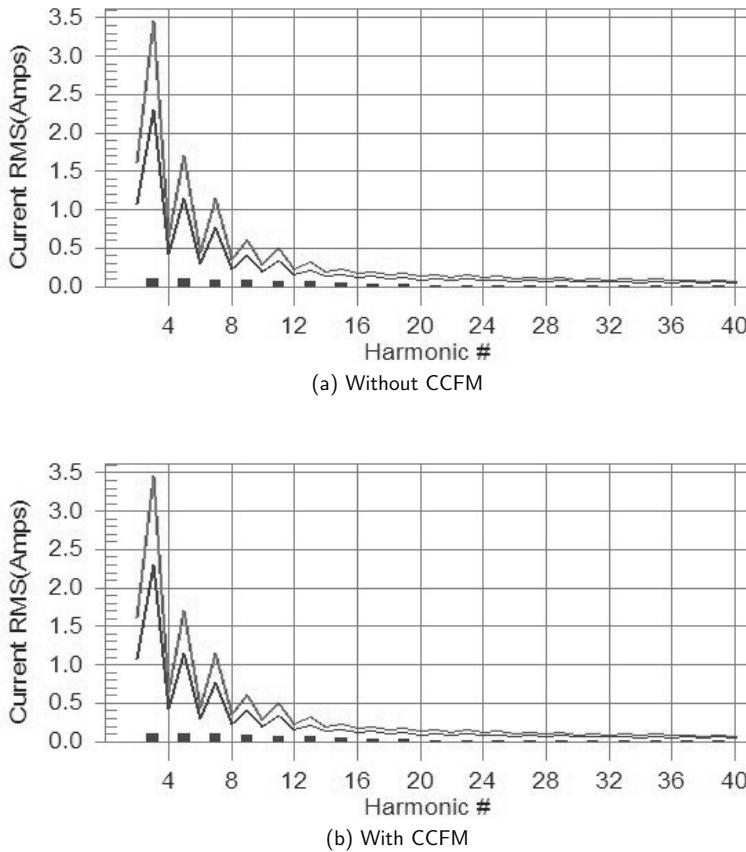

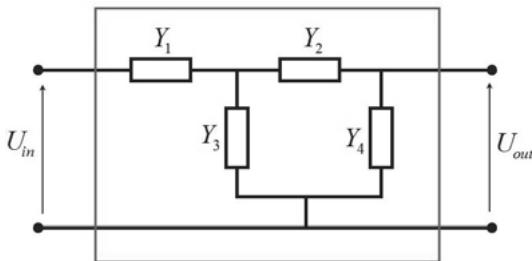

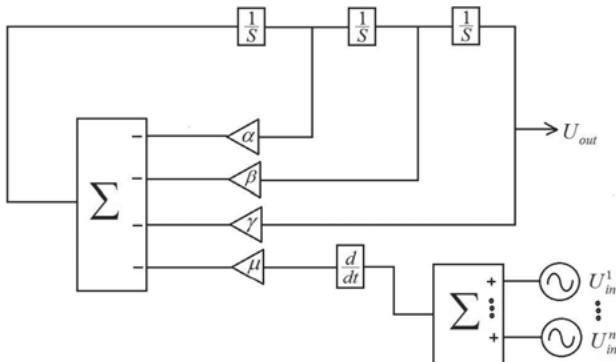

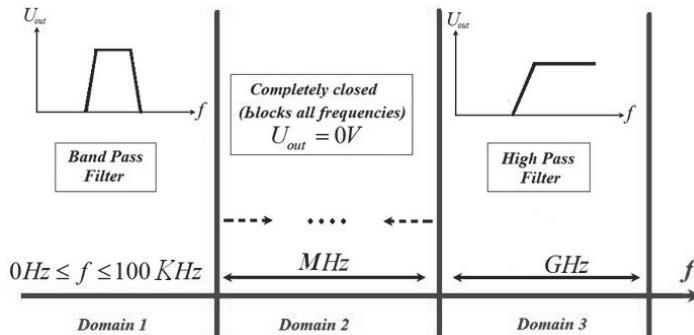

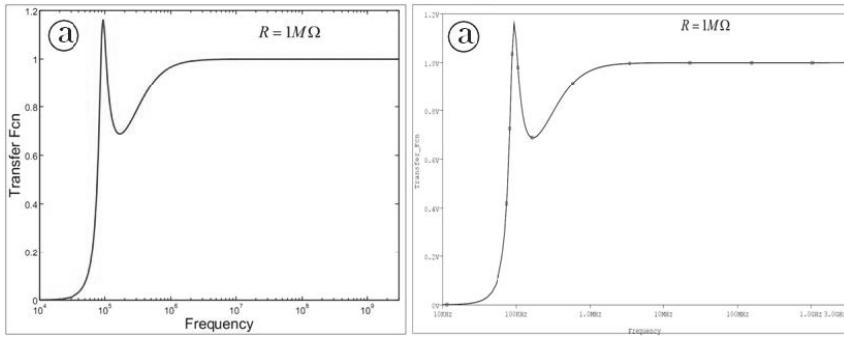

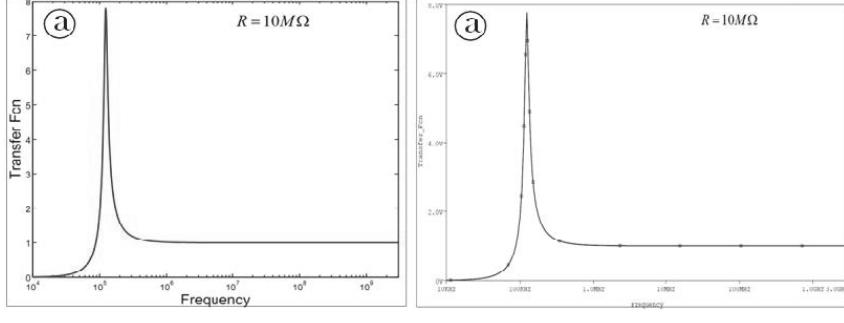

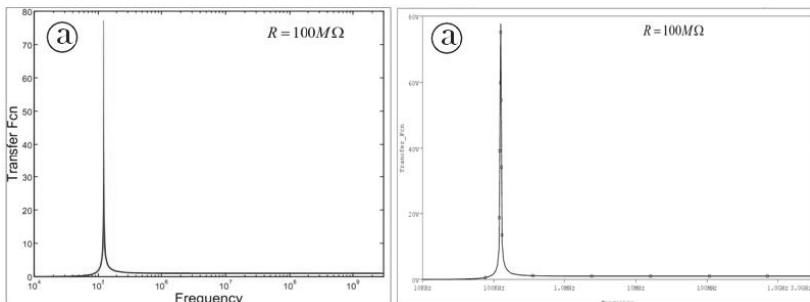

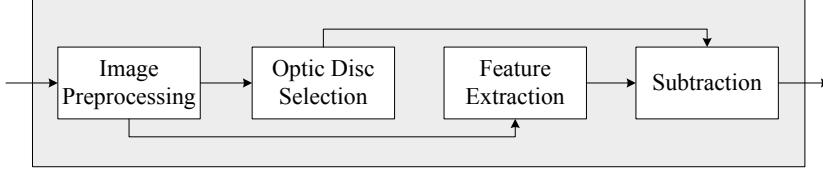

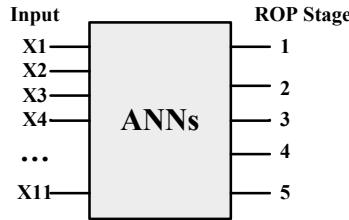

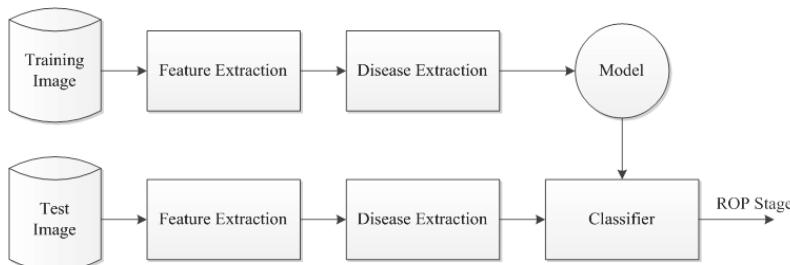

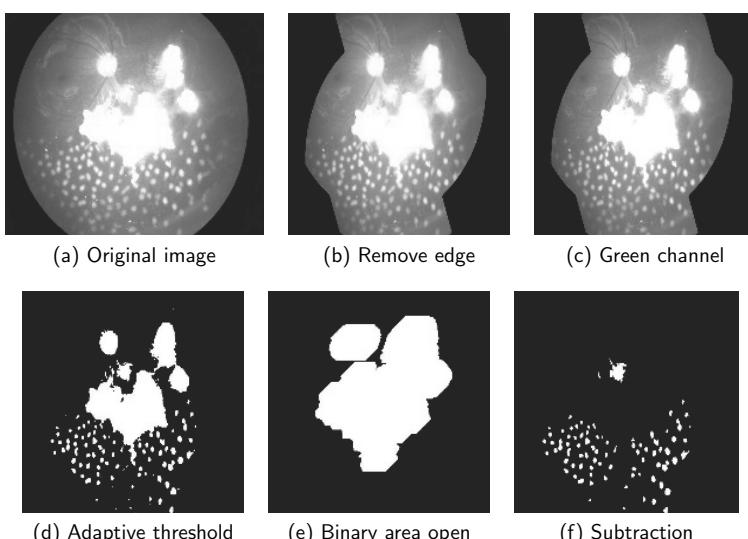

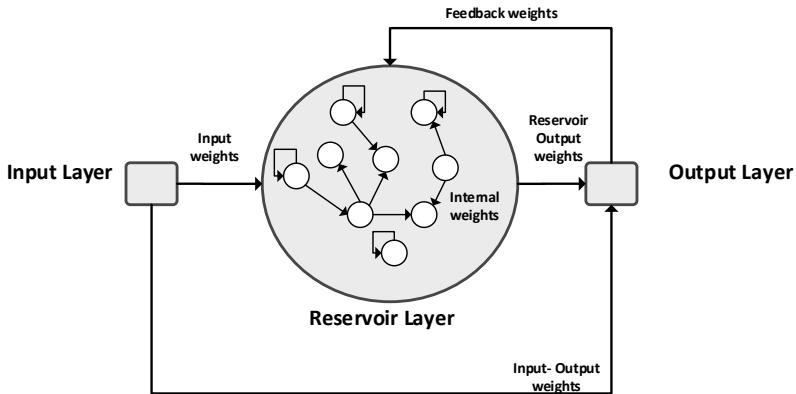

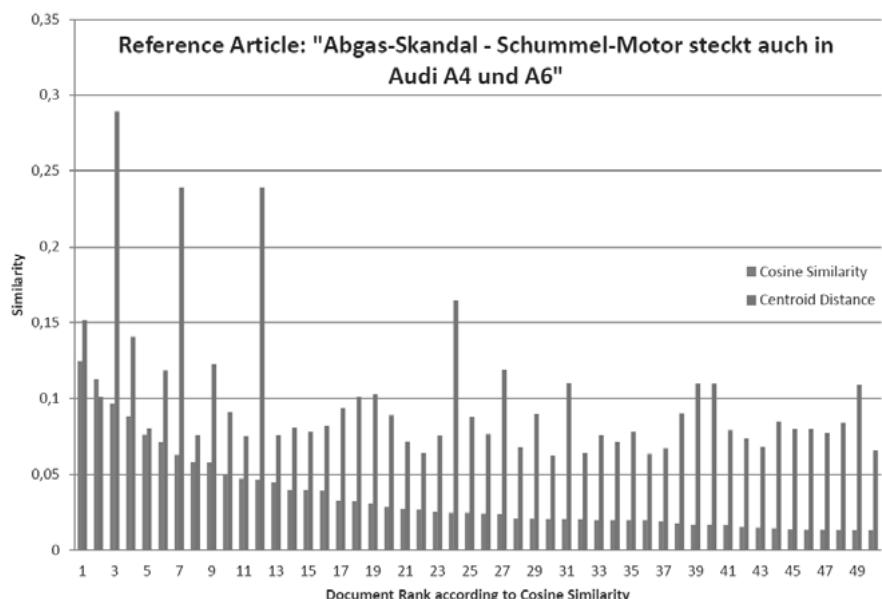

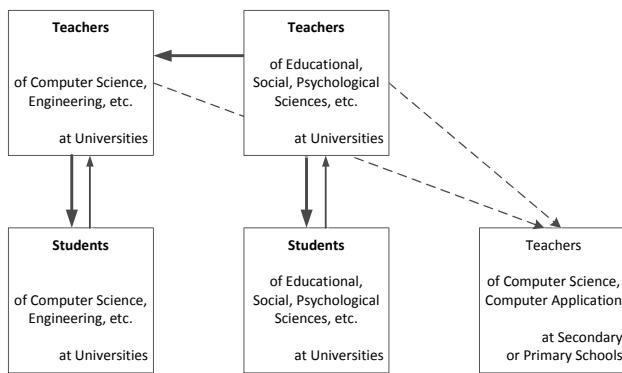

| R 9         | -   | -   | +    |